# Worst-case Performance Analysis Under Random Telegraph Noise Induced Threshold Voltage Variability

A.K.M. Mahfuzul Islam Institute of Industrial Science The University of Tokyo Meguro-ku, Tokyo, Japan Email: mahfuzul@iis.u-tokyo.ac.jp Hidetoshi Onodera

Graduate School of Informatics

Kyoto University

Sakyo-ku, Kyoto, Japan

Email: onodera@vlsi.kuee.kyoto-u.ac.jp

Abstract—RTN induced threshold voltage distribution has a long tail that can degrade the worst-case distribution severely. In this paper, we analyze the effect of RTN on worst-case performance based on variability models extracted from a 65 nm silicon-on-thin-body low threshold voltage process. Monte Carlo based simulation results reveal that with the lowering of supply voltage, RTN can degrade the worst-case delay by more than 10 % when the number of critical paths is 10. The worst-case delay degradation can go as high as 100 % if the critical path number increases to 100. Because of the RTN induced threshold voltage fluctuation, several outliers appear at near/subthreshold operation. Considering RTN amplitude can increase at weak-inversion operation, low-voltage operation needs careful consideration of RTN.

# I. INTRODUCTION

With technology scaling, random telegraph noise (RTN) has become an increasing concern [1, 2]. There are reports of RTN effects on the performance of SRAMs [3], ring oscillators (RO) [4], and Flash memories [5]. At low voltage operation, frequency fluctuation of 10.4 % has been reported for a 40 nm process [4]. It is known that worst-case distribution of random variables is sensitive to long tail in the parent distribution. RTN induced  $\Delta V_{\rm T}$  distribution is reported to follow Lognormal or Exponential distribution meaning the distribution has a long tail. On the other hand, random dopant fluctuation (RDF) induced WID random variation is reported to follow a Normal distribution [6, 7]. Normally, RDF induced WID random variation is much larger than that induced by RTN. A transistor encounters both of the within-die (WID) random variation and RTN induced random variation simultaneously. As a result, the total variation is a statistical sum of WID random variation and RTN induced random variation. It is not clear whether RTN can make a large impact on the worst-case distribution when both of the WID variation and RTN are considered. Therefore, a theoretical analysis of worst-case performance is useful to asses the impact of RTN on performance degradation.

In analyzing the effect of RTN on performance, following difficulties arise.

1) Total  $\Delta V_{\rm T}$  distribution of transistors is the sum of Normal (WID) and Lognormal (RTN) distributions.

2) At low voltage, because of the non-linearity in delay against  $\Delta V_{\rm T}$ , suitable distribution to represent the delay variation is difficult to define.

RTN induced  $\Delta V_{\mathrm{T}}$  variation is much smaller than WID  $\Delta V_{\rm T}$  variation. Even though, RTN is reported to affect the performance of SRAM and Flash memories at low-voltage operation where large number of devices operate in parallel. Besides, anomalous current fluctuations have been reported because of RTN at sub-threshold operation [8]. Our hypothesis is that the long tail in the RTN amplitude distribution causes anomaly in the performance distribution. According to our knowledge, there is no report on the theoretical analysis of worst-case performance distribution considering RTN. We, therefore, attempt to provide a theoretical framework to asses the impact of RTN on worst-case distributions. In this paper, we focus firstly on the worst-case  $\Delta V_{\rm T}$  distributions. Then, we perform Monte Carlo based analysis to obtain worst-case delay distribution using analytical delay models. We investigate the effect of supply voltage on the worst-case distributions. The WID and RTN induced  $\Delta V_{\mathrm{T}}$  distribution models we used in this analysis are derived from a 65 nm silicon-on-thinbody low threshold voltage process. We use skewed ring oscillators (RO) to capture the delay fluctuations and extract variability models for  $\Delta V_{\rm T}$  distributions. Our delay analysis based on the extracted variability models show that worst-case performance degradation due to RTN can be more than 10 % at low-voltage operation. Because of the long tail induced by the RTN, the worst-case performance is sensitive to parallel number of paths. For a parallel number of 100, the worstcase delay degradation due to RTN can be as high as 100 % at near/sub-threshold operation. Therefore, it is important to accurately characterize RTN variability and its impact on circuit performance especially for low-voltage operation.

The remainder of the paper is organized as follows. We describe a variability modeling methodology considering both of the WID variation and RTN induced variation in Sec. II. In Sec. III, we present maximum value distribution theory and its properties that are the base of our analysis. We then present

our analysis results in Sec. IV. Finally, we put our concluding remarks in Sec. VI.

#### II. VARIABILITY MODELING

## A. Modeling

We need to consider both of the RDF induced within-die static  $\Delta V_{\rm T}$  variation and RTN induced  $\Delta V_{\rm T}$  variation. Thus, the  $V_{\rm T}$  of a transistor can be expressed as follows.

$$V_{\rm T} = V_{\rm T0} + \Delta V_{\rm T.WID} + \Delta V_{\rm T.RTN},\tag{1}$$

$$\Delta V_{\rm T} = \Delta V_{\rm T,WID} + \Delta V_{\rm T,RTN}.$$

(2)

Note that we have omitted the global die-to-die variation component and assume that  $V_{\rm T0}$  includes the global component. Furthermore, we assume that most of the current fluctuations are caused by the change in transistor threshold voltage for simplicity. Here, we focus on the worst-case distribution based on the statistical max operation. In order to obtain the total  $\Delta V_{\rm T}$  distribution, we need to confirm the following properties.

- 1) Suitable distributions for WID variation and RTN induced  $\Delta V_{\rm T}$  variation, and

- 2) Correlation between the WID and RTN variations.

There is one significance difference between the two types of variations of WID and RTN when estimating performances of a delay path for example. WID variation is static and thus statistical sum operation can be performed. However, RTN is a dynamic phenomenon where current fluctuations occur at different probabilities at different transistors. Therefore, a straight forward statistical sum operation cannot be performed. In this paper, we make the following approximation so that we can treat RTN induced  $\Delta V_{\rm T}$  variation as static.

Assumption 1: Given enough time of operation, there exist at least one time frame where all fluctuations occur simultaneously in a delay path.

The above approximation will result in pessimistic evaluation of performance distributions. None the less, analysis based on the above approximation will give us useful insights. Now that we treat both of the WID and RTN  $\Delta V_{\rm T}$  distributions as static, we can perform convolution to obtain the overall  $\Delta V_{\rm T}$  distribution given that  $\Delta V_{\rm T,WID}$  and  $\Delta V_{\rm T,RTN}$  are independent to each other. The threshold voltage  $V_{\rm T}$  of a transistor is related to the average surface potential, whereas RTN amplitude depends on the exact surface potential value under the trap. Therefore, it is expected that no significant correlation exists between transistor  $V_{\rm T}$  and RTN induced  $\Delta V_{\rm T}$ . Our measurement results also validate this fact which will be presented later in the section. Literature reports also support the assumption [9]. Thus, WID random variation and RTN induced  $\Delta V_{\rm T}$  can be treated as independent to each other.

## B. Measurement Circuit

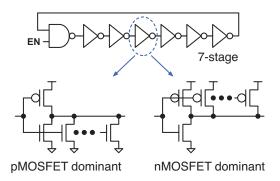

In this paper, two different types of skewed ROs are used to evaluate WID random variation and RTN.

RO type #1 (pMOSFET dominant): small pMOSFET and large nMOSFET.

Fig. 1: Ring oscillator structure to characterize pMOSFET and nMOSET RTN. Large skewed inverter cells are used. Different P/N ratio is utilized to decouple nMOSFET and pMOSFET RTN.

# RO type #2 (nMOSFET dominant): large pMOSFET and small nMOSFET.

The chip contains 208 instances of identical ROs to characterize statistical properties. Each RO instance is measured for 10 s with an integration time of 1 ms to capture RTN characteristics. Supply voltage is varied from 0.4 V to 1.0 V. The details of the test chip is explained in [10].

In order to estimate  $\Delta V_{\rm T}$  distributions from the measured  $\Delta d/d$  distributions, A linear model as Eq. (3) based on simulation based sensitivity coefficients is utilized.

$$\frac{\Delta d}{d} = \sum_{i=1}^{N_{\text{Tr}}} \left( k_i \cdot \Delta V_{\text{T},i} \right). \tag{3}$$

Here,  $N_{\rm Tr}$  is the number of transistors in the RO.  $k_i$  is sensitivity coefficient which can be calculated by SPICE simulation using MOSFET model provided by the foundry.

In RO #1, the delay fluctuations will be dominated by the smaller pMOSFETs. Similarly, in RO #2, the delay fluctuations will be dominated by the smaller nMOSFETs. Thus, utilizing the differences in the variability sources, statistical fitting on the measured distribution can be performed to estimate the parameters of  $\Delta V_{\rm T}$  distributions [10].

### C. WID Variability

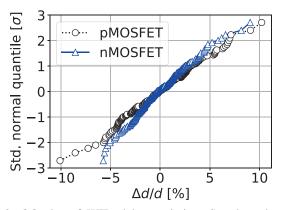

It is reported that static process  $V_{\rm T}$  distribution follows Normal distribution up to  $\pm 5\sigma$  for planar and FinFET technologies [6, 7]. The normality of WID  $\Delta V_{\rm T}$  variability is important for yield and performance analysis of circuits with large number of devices such as the SRAM. For our target process, we extract the WID random variation of pMOSFET and nMOSFET from RO frequency variations. Fig. 2 shows QQ plots of delay variations for pMOSFET and nMOSFET dominant ROs. Supply voltage is set to 0.6 V such that the transistor operate in strong-inversion. In this operating region, the delay change against  $V_{\rm T}$  change is linear. Thus, as the plot is a near straight line, we confirm that the WID random variation follows normal distribution. We then estimate the  $\mu$  and  $\sigma$  of Normal distributions for pMOSFET and nMOSFET using

Fig. 2: QQ-plot of WID delay variation. Supply voltage is 0.6 V.

which the simulated distribution matches with the measured distributions. The resulted Normal distribution parameters are  $\mu=0$  mV and  $\sigma=15$  mV. The transistor  $V_{\rm T}$  is near 0.3 V in the target process.

## D. RTN Amplitude Variability

To assess whether RTN induced  $\Delta V_{\rm T}$  distribution is valid for maximum value statistics, we need a theoretical model and experimental results that support the theory. A simple model for RTN amplitude for a single trap based on surface potential fluctuation is proposed where the  $\mu$  and  $\sigma$  of a Lognormal distribution,  $\mathcal{LN}(\mu, \sigma^2)$  is expressed by Eqs. (4) and (5) [11].

$$\mu_{\ln(\Delta V_{\rm T})} = \ln\left(\frac{q}{C_{\rm ox}WL}\right), \tag{4}$$

$$\sigma_{\ln(\Delta V_{\rm T})} = \frac{q}{kT} \times \sigma_{\phi_s}. \tag{5}$$

$$\sigma_{\ln(\Delta V_{\rm T})} = \frac{q}{kT} \times \sigma_{\phi_s}.$$

(5)

The overall  $\Delta V_{\rm T}$  probability distribution is then computed as follows.

$$P_1(x) = \frac{1}{x\sigma\sqrt{2\pi}} \cdot e^{-\frac{(\ln x - \mu)^2}{2\sigma^2}},\tag{6}$$

$$P_N(x) = \int_{-\infty}^{\infty} P_{N-1}(x-t) \cdot P_1(t) \cdot dt, \qquad (7)$$

$$a_N = \frac{\lambda^N e^{-N}}{N!}, \qquad (8)$$

$$a_N = \frac{\lambda^N e^{-N}}{N!},\tag{8}$$

$$P(x) = a_0 \delta(x) + \sum_{i=1}^{N} a_i P_i(x).$$

(9)

Here,  $P_1(x)$  is the probability distribution function (PDF) for a single trap  $\Delta V_{\rm T}$  and  $P_N(x)$  is the PDF of total  $\Delta V_{\rm T}$  because of N traps.  $a_N(x)$  is probability mass function (PMF) for the number N of traps. P(x) is the PDF of overall  $\Delta V_{\rm T}$ incorporating the trap number distribution.

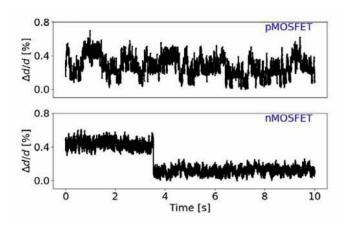

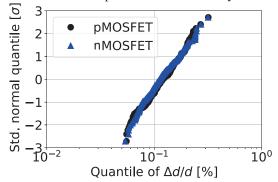

Fig. 3 shows two waveform samples for RO oscillation period. Fig. 4 shows OO plots of  $\Delta d/d$  for pMOSFET and nMOSFET dominant ROs. X-axis is plotted in logarithm scale. Y-axis shows the standard normal quantile. Straight lines in the QQ plots mean that the distributions follow Lognormal distributions. Assuming  $\Delta V_{\mathrm{T}}$  distribution follow a Lognormal

Fig. 3: Waveform examples RTN induced delay fluctuations.

Fig. 4: QQ plot of RTN induced  $\Delta d/d$  for pMOSFET and nMOSFET dominant ROs.

distribution,  $\mathcal{LN}(\mu, \sigma^2)$ ,  $\mu$  and  $\sigma$  are extracted to be -0.15and  $\sigma = 0.90$ , respectively. Similar  $\Delta V_{\rm T}$  distributions are estimated for both of the pMOSFET and nMOSFET.

As large tail in the RTN induced  $\Delta V_{\rm T}$  amplitude distribution originates from the surface potential variability [12], we assume that the logarithm of  $\Delta V_{\rm T}$  has Normality up to  $5\sigma$  at least. Assuming surface potential variability of  $\sigma_{\phi_s} = 20 \text{ mV}$ [13], the values of  $\mu$  and  $\sigma$  from Eqs. (4) and (5) results in -0.33 and 0.77 at T = 298 K. W = 140 nm, L = 60 nm, gate oxide thickness,  $T_{\rm ox}=1.3~{\rm nm}$  and  $\epsilon_r=3.9$  is assumed in this calculation. Then considering a Poisson distribution Poiss( $\beta$ ) with  $\beta = 1.2$  [9], we obtain a distribution according to Eq. (9). Fitting a Lognormal distribution to the obtained final distribution yields  $\mu = -0.14$  and  $\sigma = 0.98$ . Thus, the reported Lognormal model for our process supports the theoretical assumptions.

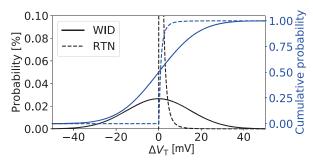

Finally, we show a comparison between the distributions to represent WID random variation and RTN induced  $\Delta V_{\rm T}$ variation in Fig. 5. The left hand Y-axis shows the probability and the right hand Y-axis shows the cumulative probability of the  $\Delta V_{\rm T}$ . It is clear that RTN induced  $\Delta V_{\rm T}$  is much smaller than the WID random  $\Delta V_{\rm T}$  variation. However, we will show in Sec. IV that the long tail in the RTN induced  $\Delta V_{\mathrm{T}}$  distribution can significantly degrade the worst-case performance.

Fig. 5:  $\Delta V_{\mathrm{T}}$  distributions for WID and RTN.

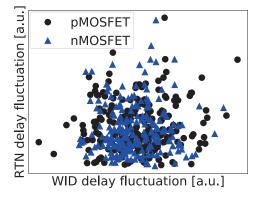

Fig. 6: Correlation between WID delay variation and RTN induced delay fluctuation. No correlation is observed.

## E. Correlation between WID and RTN Variability

As explained in Sec. II-A, it is important to verify whether WID random variation and RTN induced random variation is correlated or not. In Fig. 6, we plot RTN induced delay fluctuation against WID random delay variation for a pMOSFET dominant RO and an nMOSFET dominant RO. It is clear from the figure that no correlation exists for both of the pMOSFET and nMOSFET dominated ROs.

# III. MAXIMUM VALUE STATISTICS

Here, we show how the maximum value distribution can be obtained from the parent distributions of transistor  $\Delta V_{\rm T}$ . Let  $\{x_1, x_2, \cdots, x_N\}$  be a set of random variables with identical PDF and CDF of p(x) and P(x). The sample maximum is defined as

$$Maximum M = \max(x_1, x_2, \cdots, x_N). \tag{10}$$

If the joint probability distribution  $P(x_1, x_2, \dots, x_N)$  is known, then the cumulative distribution of maximum M can be expressed as follows.

$$Q_N(x) = \text{Prob}[M \le x, N] \tag{11}$$

$$= \operatorname{Prob}[x_1 \le x, x_2 \le x, \cdots, x_N \le x] \tag{12}$$

$$= \int_{\infty}^{x} \int_{\infty}^{x} \cdots \int_{\infty}^{x} dx_1 dx_2 \cdots dx_N P(x_1, x_2, \cdots, x_N).$$

For independent and identical random variables, the joint PDF factorises and we get

$$Q_N(x) = \left[ \int_{-\infty}^x \mathrm{d}x \ p(x) \right]^N = \left[ 1 - \int_x^\infty \mathrm{d}x \ p(x) \right]^N. \tag{14}$$

According to Gnedenko's classical law of extremes,  $Q_N(x)$  approaches the following limiting form.

$$Q_N(x) \xrightarrow[x \to \infty, N \to \infty]{z = (x - a_N)/b_N \text{ fixed}} F(\frac{x - \mu}{\sigma}) = F(z). \tag{15}$$

For a parent distribution with Gaussian like tail, F(z) can be approximated by Gumbel distribution [14].

$$F(x; \mu, \sigma) = e^{-e^{(x-\mu)/\sigma}}, \tag{16}$$

$$f(x; \mu, \sigma) = \frac{1}{\sigma} \times e^{(x-\mu)/\sigma} \times e^{-e^{(x-\mu)/\sigma}}.$$

(17)

Thus, for large number of parallel devices, a Gumbel distribution can be used to model the worst-case distribution. If Monte Carlo simulation is performed, Gumbel distribution can be obtained by fitting the parameters to the simulated distribution.

## IV. Worst-Case $\Delta V_{\mathrm{T}}$ Distribution

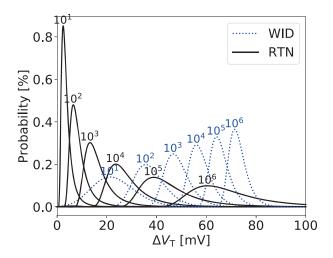

For circuits like SRAM for example, large number of transistors operate in parallel. We can call the logic depth to be 1 in this case. For these circuits, maximum value distribution of  $\Delta V_{\rm T}$  is of great importance. Therefore, we analyze the worst-case  $\Delta V_{\rm T}$  distributions with and without the effect of RTN. First, we demonstrate the impact of tail in the parent distribution on the resultant worst-case distribution. Fig. 7 shows the comparison between maximum value distributions when either WID random variation or RTN induced random variation is considered. Dotted lines show the distributions for WID random variations. Solid lines show the distributions for RTN random variations. Maximum distributions are shown for different transistor numbers in parallel. When the transistor number is 10, maximum distribution of  $\Delta V_{\rm T}$  induced by RTN is much smaller than that induced by WID random variation. However, with the increase of transistor number, the worst-case distribution degrades rapidly for the case of RTN compared with the case of WID random variation. Thus, long tail in the parent distribution has a severe effect on the worstcase distribution. Therefore, although the variation due to RTN of a single transistor may be negligible, its impact on circuits with large number of transistors should not be ignored.

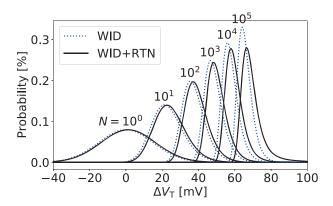

Fig. 7 shows the worst-case  $\Delta V_{\rm T}$  distribution for two cases of WID and RTN variations separately. But a transistor in the chip encounters both the WID and RTN variations simultaneously. Therefore, the variation model of Eq. (2) is of relevant to analyze the worst-case distributions. Fig. 8 shows the worst-case  $\Delta V_{\rm T}$  distributions for two new cases. The first case corresponds to WID random variation only. The second case represents the scenario when both WID and RTN variations are involved. For a single transistor  $N=10^{0}$ , the difference between the worst-case distributions for the two cases are insignificant. However, with transistor number crossing  $10^{3}$ , clear deviation between the two cases becomes

Fig. 7: Maximum distributions of  $\Delta V_{\rm T}$  with two different parent distributions of Normal and Lognormal for different transistor count, N. Normal distribution represents RDF induced process variation whereas Lognormal distribution represents RTN induced  $\Delta V_{\rm T}$  variability.

Fig. 8: Maximum distributions of  $\Delta V_{\rm T}$  for different transistor count, N when both of the static variation and RTN induced variation is considered.

visible. For transistor number  $N=10^5$ , long tail appears in the worst-case distribution for the second case. This long tail may cause malfunctions in circuits. As a result, for circuit with large number of parallel devices, adequate margin is required to ensure high yield.

# V. WORST-CASE DELAY DISTRIBUTION

## A. Delay Model

The delay of a single stage in a delay path can be expressed by Eq. (18).

$$\tau = \frac{C_{\rm L} V_{\rm DD}}{I_{\rm D}}.\tag{18}$$

Here,  $\tau$  is the gate delay,  $C_{\rm L}$  is load capacitance,  $V_{\rm DD}$  is supply voltage, and  $I_{\rm D}$  is transistor ON current. The total delay, d of a delay path consisting of  $L_{\rm d}$  logic gates is then expressed as follows.

$$d = \sum_{i=1}^{L_{\rm d}} \tau_i. \tag{19}$$

Here,  $\tau_i$  is the delay of *i*-th stage. For modeling digital circuit switching delay, the  $\alpha$ -power law current model of Eq. (20) is widely used [15].

$$I_{\rm D} = b_1 \cdot \frac{W}{L} \cdot (V_{\rm DD} - V_{\rm T})^{\alpha} \,. \tag{20}$$

Here,  $b_1$  is a constant related to technology, W is gate width, and L is gate length. The value of  $\alpha$  is typically 1.3 for scaled processes. The model equation of Eq. (20) is suitable for analyzing logic delay when the transistors operate at strong-inversion. For transistors operating at weak-inversion, the following current model is widely used.

$$I_{\rm D} = b_2 \cdot \frac{W}{L} \cdot \exp\left(\frac{V_{\rm DD} - V_{\rm T}}{n U_T}\right).$$

(21)

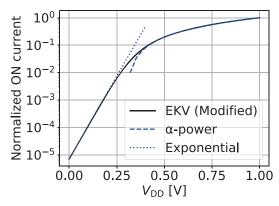

Here,  $b_2$  is a technology related fitting parameter, n is the sub-threshold swing parameter and  $U_T$  is the thermal voltage. Using current models based on the operating region may cause inconsistent result across the operating regions. Therefore, to assess the variability effect for all the regions, a model that is continuous and valid from weak-inversion to strong-inversion operation is required. Such a model is the EKV model [16]. The original EKV model is intended for low-voltage analog circuit design, where velocity saturation is not considered. In order to model the velocity saturation effect, we have used a modified version of Eq. (22).

$$I_{\rm D} = b_3 \cdot \frac{W}{L} \cdot \ln \left[ 1 + \exp\left(\frac{V_{\rm DD} - V_{\rm T}}{\alpha \, n \, U_T}\right) \right]^{\alpha}.$$

(22)

Here,  $b_3$  is a technology related parameter. The validity of the model Eq. (22) is shown in Fig. 9. Transistor ON current across  $V_{\rm DD}$  is shown in the figure for the three models of  $\alpha$ -power law model, the modified EKV model and the exponential model for weak-inversion. The  $\alpha$ -power law model becomes inaccurate when  $V_{\rm DD}$  approaches  $V_{\rm T}$ . Consequently, the exponential model becomes inaccurate when  $V_{\rm DD}$  crosses  $V_{\rm T}$ . The EKV model is able to represent both the strong-inversion and weak-inversion currents as well as the region in between. There, delay analysis using EKV model is appropriate to assess the relative delay variations across the different operation regions.

# B. Worst-case Delay Distribution

1) Analysis Method: Overall  $\Delta V_{\rm T}$  distribution including both of the WID random variation and RTN is a statistical sum of a Normal and a Lognormal distribution. Thus finding a valid distribution to represent the overall  $\Delta V_{\rm T}$  distribution is challenging. In this paper, we perform Monte Carlo simulation by generating random  $\Delta V_{\rm T}$  for WID and RTN induced  $\Delta V_{\rm T}$

Fig. 9: Comparison between different current models.

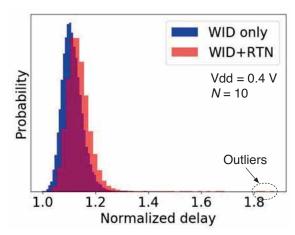

Fig. 10: Histograms of simulated delay. Outliers appear in the case of considering RTN induced  $\Delta V_{\rm T}$  variation.

and simulate the corresponding delay using Eqs. (18) and (22). We then calculate the 99.7 percentile delay value in the maximum delay distribution as the worst-case delay. 50,000 maximum delay samples are simulated in our experiment.

2) Results: Now, we analyze the worst-case distribution for delay paths considering the RTN along with WID random variation. Distributions for two cases are simulated where in the first case only the WID random variation is considered. In the second case, RTN random variation is also considered with the WID variation. Fig. 10 shows the histogram of the maximum delay for the two cases. The parallel path number N is 10 is this case. The logic depth that is the number of logic cells in the path is set to 10 here.  $V_{\rm DD}$  is 0.6 V. The 99.7 percentile value in the worst-case distribution increases by more than 5 % with the inclusion of RTN variation. However, as shown in the figure, multiple outliers appear in the second case where RTN is considered. Because of the long tail property in the RTN induced  $\Delta V_{\rm T}$  distribution, anomalous delay behavior occurs. When only WID is considered, no such anomaly was found.

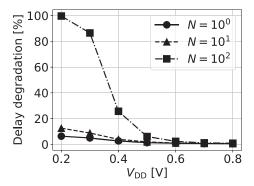

Fig. 11: Increase of worst-case delay due to RTN against that without RTN.

# C. $V_{\rm DD}$ Dependency

Fig. 11 plots the increase of 99.7 percentile delay value caused by the RTN variation against the supply voltages. When  $V_{\rm DD}$  is much higher than  $V_{\rm T}$ , the increase is below 1 %. Thus, we may not need to worry much on the effect of RTN on worst-case delay estimation. Worst-case delay estimation considering only the WID random variation might suffice. With the decrease of  $V_{\rm DD}$ , the delay degradation increases. At 0.3 V, the delay degradation is more than 10 % when the parallel path number is 10. With the increase of parallel path number to 100, the delay degradation is accelerated and we observe delay degradation of near 100 % at sub-threshold operation. At low-voltage operation, there remains a possibility that the circuit may malfunction in some cases. Additional margin to account RTN induced delay degradation is a must for low-voltage operation.

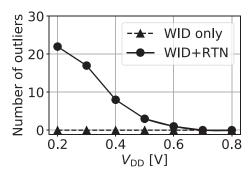

#### D. Outliers

One key characteristic found in the worst-case delay analysis is the appearing of significant number of outliers in the distributions. To quantify the number of outliers, we define the threshold of outlier to be 1.5 times the worst-case delay. Fig. 12 shows the number of outliers against the supply voltage. When RTN is not considered, no outliers exist in the distribution. However when RTN is considered, the outliers begin to appear with the decrease of  $V_{\rm DD}$ . Therefore, at low-voltage operation some anomalous delay can be found making low-voltage operation further challenging. Our simulation results are supported by some of the literature reports [4, 8]. We provide for the first time a thorough analytical analysis to explain the properties.

#### VI. CONCLUSION

In this paper, we have evaluated worst-case  $\Delta V_{\rm T}$  and delay distributions under the variability induced by both of the random dopant fluctuation (RDF) and random telegraph noise (RTN). Our analysis is based on measurement results of delay fluctuations from a 65 nm silicon-on-thin-body low- $V_{\rm T}$  process. Analysis results show that at strong inversion operation, the consideration of RTN induced  $\Delta V_{\rm T}$  variability degrades the worst-case delay by only less than 1 %. However,

Fig. 12: Number of outliers against supply voltage.

when the supply voltage is lowered below the transistor threshold voltage, the performance degradation increases to more than 10 %. When the number of parallel paths is 100, the performance degradation can reach near 100 %. We have observed significant number of outliers appear when RTN is considered. Thus, we surmise that RTN induced  $\Delta V_{\rm T}$  variability will play a significant role at low supply voltage operation. As the underlying cause for the RDF and RTN induced variability is the surface potential fluctuation, the analysis results can be scaled to a finer process.

#### ACKNOWLEDGMENT

The authors would like to thank Masashi Oka of Kyoto University for helping the measurements. The VLSI chip in this study was fabricated in the chip fabrication program of the VLSI Design and Education Center (VDEC), the University of Tokyo, in collaboration with Renesas Electronics. This work has been supported in part by JSPS KAKENHI 25280014 and 16H01713.

### REFERENCES

- [1] M. Kirton and U. M. in Physics, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise," *Advances in Physics*, vol. 38, no. 4, pp. 367–468, 1989.

- [2] N. Tega, H. Miki, F. Pagette, D. Frank, M. Rooks, W. Haensch, and K. Torii, "Increasing threshold voltage variation due to random telegraph noise in FETs as gate lengths scale to 20 nm," *Symposium on VLSI Technology Digest of Technical Papers*, pp. T50–T51, 2009.

- [3] H. Qiu, T. Mizutani, Y. Yamamoto, H. Makiyama, T. Yamashita, H. Oda, S. Kamohara, N. Sugii, T. Saraya, M. Kobayashi, and T. Hiramoto, "Impact of random telegraph noise on write stability in Silicon-on-Thin-BOX (SOTB) SRAM cells at low supply voltage in Sub-0.4V regime," Symposium on VLSI Technology Digest of Technical Papers, pp. T38–T39, 2015.

- [4] T. Matsumoto, K. Kobayashi, and H. Onodera, "Impact of random telegraph noise on CMOS logic delay uncertainty under low voltage operation," in *IEEE Electron Devices Meeting*, 2012, pp. 25.6.1–25.6.4.

- [5] A. Ghetti, C. Compagnoni, A. S. Spinelli, and A. Visconti, "Comprehensive analysis of random telegraph

- noise instability and its scaling in DecaNanometer flash memories," *IEEE Transactions on Electron Devices*, vol. 56, no. 8, pp. 1746–1752, 2009.

- [6] T. Tsunomura, A. Nishida, F. Yano, A. T. Putra, K. Takeuchi, S. Inaba, S. Kamohara, K. Terada, T. Hiramoto, and T. Mogami, "Analyses of 5σ Vth Fluctuation in 65nm-MOSFETs using Takeuchi Plot," in *Symposium* on VLSI Technology Digest of Technical Papers, 2008, pp. 156–157.

- [7] M. Giles, A. N. Radhakrishna, D. Becher, A. Kornfeld, K. Maurice, S. Mudanai, S. Natarajan, P. Newman, P. Packan, and T. Rakshit, "High sigma measurement of random threshold voltage variation in 14nm logic FinFET technology," in *Symposium on VLSI Technology Digest* of Technical Papers, 2015, pp. T150–T151.

- [8] J. Campbell, L. yu, K. Cheung, J. Qin, J. Suehle, A. Oates, and K. Sheng, "Large random telegraph noise in Sub-Threshold operation of Nano-Scale nMOSFETs," in *IEEE International Conference on IC Design and Technology*, 2009, pp. 17–20.

- [9] A. K. M. M. Islam, T. Nakai, and H. Onodera, "Statistical analysis and modeling of random telegraph noise based on gate delay measurement," *IEEE Transactions on Semi*conductor Manufacturing, vol. 30, no. 3, pp. 216–226, 2017.

- [10] A. K. M. M. Islam and H. Onodera, "Effect of supply voltage on random telegraph noise of transistors under switching condition," in *IEEE/ACM International Sympo*sium on Power and Timing Modeling, Optimization and Simulation (PATMOS), 2017, pp. 1–8.

- [11] K. Sonoda, K. Ishikawa, T. Eimori, and O. Tsuchiya, "Discrete dopant effects on statistical variation of random telegraph signal magnitude," *IEEE Transactions on Electron Devices*, vol. 54, no. 8, pp. 1918–1925, 2007.

- [12] A. Asenov, R. Balasubramaniam, A. Brown, and J. Davies, "RTS amplitudes in decananometer MOS-FETs: 3-D simulation study," *IEEE Transactions on Electron Devices*, vol. 50, no. 3, pp. 839–845, 2003.

- [13] G. Slavcheva, J. Davies, A. Brown, and A. Asenov, "Potential fluctuations in metal-oxide-semiconductor field-effect transistors generated by random impurities in the depletion layer," *Journal of Applied Physics*, vol. 91, no. 7, pp. 4326–4334, 2002.

- [14] S. Majumdar and A. Pal, "Extreme value statistics of correlated random variables," *arXiv preprint arXiv:1406.6768*, 2014.

- [15] T. Sakurai and A. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," *IEEE Journal of Solid-State Circuits*, vol. 25, no. 2, pp. 584–594, 1990.

- [16] C. C. Enz, F. Krummenacher, and E. A. Vittoz, "An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications," *Analog integrated circuits and Signal Processing*, vol. 8, no. 1, pp. 83–114, 1995.