# Inhomogeneous Ring Oscillator for WID Variability and RTN Characterization

Shuichi Fujimoto†, Islam A.K.M Mahfzul†, Takashi Matsumoto†, and Hidetoshi Onodera†‡ †Graduate School of Informatics, Kyoto University, ‡JST, CREST E-Mail: {fujimoto,mahfuz,tmatsumoto,onodera}@vlsi.kuee.kyoto-u.ac.jp, TEL: +81-75-753-5335, FAX: +81-75-753-5343

Abstract—We propose an inhomogeneous ring oscillator (RO) whose performance is strongly influenced by a small set of transistors for characterizing transistor-by-transistor variability. Performance sensitivities of the transistors are enhanced by inserting a "singular point" into a homogeneous RO. Proposed ROs have been embedded in a 65nm RO-array test structure, and it is verified that the proposed ROs are highly sensitive to Within-Die (WID) local variability and Random Telegraph Noise (RTN). The amounts of random variation in threshold voltages( $V_{\rm thN}$  and  $V_{\rm thP}$ ) and channel length(L) are extracted from the WID frequency variation. Temporal variation of oscillation frequency due to RTN is observed in the inhomogeneous RO.

#### I. Introduction

With the progress of technology scaling, variability becomes a serious issue in LSI design. Within-die (WID) variation and temporal variation such as Random Telegraph Noise (RTN) are becoming rapidly growing problems especially in a low voltage operation where performance variability is a major obstacle for stable operation[1]. Accurate characterization of those transistor-by-transistor variability in a digital circuit is a key challenge.

To estimate or simulate the performance variation of a circuit under design, we have to extract variability information from measured variability of test structures. We therefore need a circuit structure to characterize variability of a transistor parameter in a real circuit. A possible method is to use a device-array test structure and measure the variability of each transistor performance[2]. This is the most basic method but it requires huge amount of cost in chip fabrication, measurement, and analysis. Also, the structure of a device-array is very much different from that of a real circuit composed of primitive cells. Variation of a cell-based circuit may not be reproduced in a devicearray structure. Another method is to develop an RO-array test structure and extract variability of performance by measuring oscillation frequencies[3]. Using this method, we can extract variability information appeared in a cellbased circuit.

In general, a conventional RO have a homogeneous structure. A homogeneous RO is suitable for extracting global variability such as die-to-die (D2D) variation, whereas the variability of each transistor is averaged

out and hence it is less visible. A homogeneous RO is therefore not suitable for evaluating WID variability and temporal fluctuation appeared in an individual transistor. In attempting the variability of a single transistor more visible, we propose to use a test structure of inhomogeneous ROs which will be explained in the next section. The inhomogeneity enhances WID variation and/or RTN caused by a particular transistor in the circuit. It enables the in-situ characterization of transistor variability in a typical cell-based design.

The remainder of this paper is organized as follows. In Section II, we discuss a conventional homogeneous RO and a proposed inhomogeneous RO. In Section III, we explain modeling of RO frequency variation for WID variability characterization. In Section IV, we discuss a test structure fabricated in a 65nm process and its measured results. Extracted WID variability and RTN from the test chip are also explained. Finally, Section IV concludes this paper.

## II. INHOMOGENEOUS RO FOR VARIABILITY ENHANCEMENT

In this section, we describe characteristics of a conventional homogeneous RO and a proposed inhomogeneous RO. We evaluate sensitivity of each transistor in both structures by SPICE simulation, and explain how the variability of a small set of transistors become visible in the inhomogeneous RO.

# A. Conventional Homogeneous RO

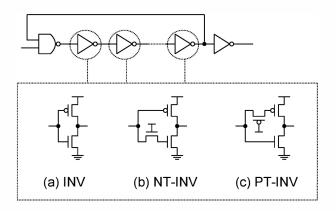

In general, a conventional RO has a homogeneous structure as shown in Fig. 1. Except for a NAND2 gate for controlling oscillation, all the inverting gates have the identical circuit structure with the same device sizes. In a scaled process, each transistor has die-to-die(D2D) and within-die (WID) variability. A common D2D variation is shared by all the transistors, and a WID variation appears in each transistor as an independent random component. In a homogeneous RO, a WID variation in each transistor is averaged out and the variability of oscillation frequency becomes small as the number of transistors in the homogeneous RO increases. On the other hand, the oscillation frequency is determined by the D2D variation. We can therefore use homogeneous ROs as process

Fig. 1. Conventional Homogeneous RO.

monitors for D2D variation[4]. Fig. 1 shows examples of homogeneous ROs. The most popular structure that use a standard inverter as the basic element is shown in Fig. 1(a) (INV). In this INV RO, D2D variations of nMOSFETs and pMOSFETs contribute to the oscillation frequency in a similar order of magnitude. We can increase/decrease the sensitivity of a particular variability parameter by modifying the basic element. Fig. 1(b) shows an inverter with an nMOS pass-transistor inserted between the input and the nMOS gate (NT-INV). This NT-INV RO is highly sensitive to the threshold voltage of nMOSFETs ( $V_{\rm thN}$ ). Similarly, Fig. 1(c) shows an inverter with a pMOS pass-transistor inserted between the input and the pMOS gate (PT-INV), which is highly sensitive to the threshold voltage of pMOSFETs ( $V_{\rm thP}$ ).

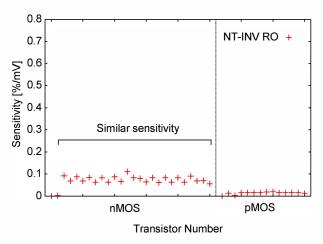

As an example of the sensitivity calculation, Fig. 2 shows the threshold sensitivity of each transistor in a 13-stage NT-INV RO derived by circuit simulation assuming a 65nm process with a 0.8 V supply voltage. As explained, sensitivities of nMOS threshold voltage ( $V_{\rm thN}$ ) are similar in magnitude and much larger than those of pMOS threshold voltage ( $V_{\rm thP}$ ). Exploiting different sensitivities for threshold voltages  $V_{\rm thN}$  and  $V_{\rm thP}$  and channel length L in INV ROs, NT-INV ROs, and PT-INV ROs, D2D components of  $V_{\rm thN}$ ,  $V_{\rm thP}$ , and L can be extracted[4]. However, the contribution of WID component in each transistor becomes small and less visible.

#### B. Proposed Inhomogeneous RO

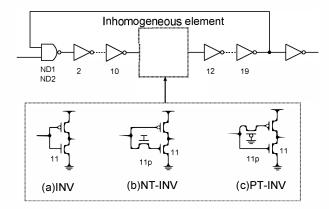

To characterize variability of each transistor, enhancing the sensitivity of a particular transistor is required. We propose an RO with an inhomogeneous structure that has a "singular point" in a conventional homogeneous circuit. Due to the inhomogeneity, each transistor has a different sensitivity. With an appropriate modification, we can enhance the variability of a small set of transistors. Fig. 3 shows an RO circuit with an inhomogeneous element. When a standard inverter (INV) is used for the element as

Fig. 2. Sensitivity of each transistor in a homogeneous NT-INV RO.

in case (a), it becomes a conventional homogeneous RO. If a pass-transistor inserted inverter (NT-INV) or PT-INV) is used for the element as in cases (b) or (c), it becomes an inhomogeneous RO. It is expected that the performance of the inhomogeneous RO can be much sensitive to the variation of particular transistors. In the following, we show simulation results to verify that the inhomogeneous RO has small number of sensitive transistors and that this circuit can be used to evaluate transistor-by-transistor variability.

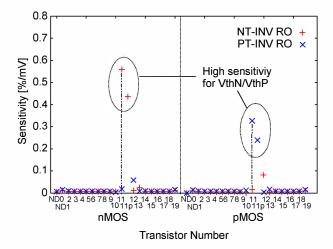

Fig. 4 shows the *V*<sub>th</sub> sensitivity of each transistor in a 19-stage nMOSFET-inserted RO(Fig. 3(b)), and a 19-stage pMOSFET-inserted RO(Fig. 3(c)), operating at 0.8 V. In both inhomogeneous ROs, the pass-transistor and the transistor pulled-up/down by the pass-transistor have very high sensitivity. The sensitivities of the two transistors in the nMOSFET-inserted RO are 90 times and 71 times higher than those of others. In the pMOSFET-inserted RO, they are 37 times and 21 times higher. Performance of inhomogeneous ROs is strongly affected by the variability of those dominant transistors. This shows that the local variability of sensitive transistors can be estimated by measuring variability of circuit performance of the inhomogeneous ROs.

#### III. MODELING OF WID VARIABILITY

If we can measure the WID variability of many ROs with the identical structure, we can further estimate the origin of the WID variability. For simplicity, we assume the sources of variability are limited to channel length (L), threshold voltage of pMOSFET  $(V_{\rm thP})$ , and that of nMOSFET  $(V_{\rm thN})$ . They are main factors of changing transistor current [5].

Assuming linear sensitivity for each variability source, the variability of oscillation frequency is given in the

Fig. 3. Ring oscillator with an inhomogeneous element.

Fig. 4. Sensitivity of each transistor in inhomogeneous ROs.

equation below.

$$F = f(V_{\text{thP1}}, V_{\text{thN1}}, L_1, V_{\text{thP2}}, \dots)$$

$$\approx \mu_F + \sum_i (K_{V_{\text{thP}i}} \Delta V_{\text{thP}i} + K_{V_{\text{thN}i}} \Delta V_{\text{thN}i} + K_{L_i} \Delta L_i) (2)$$

D2D components of L,  $V_{\text{thP}}$ , and  $V_{\text{thN}}$  variability determine the mean oscillation frequency  $\mu_F$ . WID components are represented by  $\Delta L_i$ ,  $\Delta V_{\text{thP}i}$ , and  $\Delta V_{\text{thN}i}$

As shown in Fig. 4, a few transistors have dominant sensitivities in an inhomogeneous RO. If there is a temporal variation in the threshold voltage of a dominant transistor due to RTN, it results in a noticeable variation in the oscillation frequency. Process variability of a dominant transistor also leads to a larger spread of WID frequency variation.

Assuming WID components are independent and random with Gaussian distributions, and all the nMOS-

Fig. 5. Sensitivity for WID variability source in nMOS-inserted inhomogeneous RO.

FETs/pMOSFETs have the same size. we can express the variance of oscillation frequency as the sum of variances contributed by each variation component as shown below.

$$\left(\frac{\sigma_F}{\mu_F}\right)^2 = \sum_i \left(k_{V_{\text{thP}}i}^2 \sigma_{V_{\text{thP}}}^2 + k_{V_{\text{thN}}i}^2 \sigma_{V_{\text{thN}}}^2 + k_{L_i}^2 \sigma_L^2\right). \tag{3}$$

In Eq.(3),  $k_{V_{\text{thP}i}}$ ,  $k_{V_{\text{thN}i}}$ , and  $k_{L_i}$  are the sensitivity coefficients for  $V_{\text{thP}}$ ,  $V_{\text{thN}}$  and L variation, respectively. Parameters  $\sigma_f$ ,  $\sigma_{V_{\text{thP}}}$ ,  $\sigma_{V_{\text{thN}}}$ , and  $\sigma_L$  are standard deviations of oscillation frequency,  $V_{\text{thP}}$ ,  $V_{\text{thN}}$ , and L, respectively. Index i identifies an inverting gate in the ring-oscillator where each inverter has different contribution to the oscillation frequency. As described, we derive  $k_{V_{\text{thP}i}}$ ,  $k_{V_{\text{thN}i}}$ , and  $k_{L_i}$  for each pair of transistors by circuit simulation. For example in the inhomogeneous RO in Fig. 3(b), we derive 62 sensitivity coefficients in total.

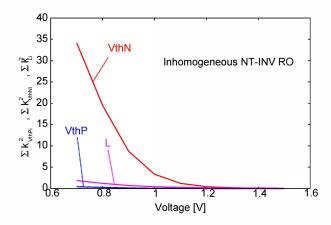

If we have an enough number of identical ROs, we can measure  $\left(\frac{\sigma_f}{\mu_f}\right)^2$ . Unknown parameters that we want to derive are  $\sigma_{V_{\text{thP}}}^2$ ,  $\sigma_{V_{\text{thN}}}^2$ , and  $\sigma_L^2$ . If we have at least 3 equations with different set of  $k_{V_{\text{thP}i}}$ ,  $k_{V_{\text{thN}i}}$ , and  $k_{L_i}$ , we can derive the unknown parameters of our interest. We can also exploit different voltage dependencies of those coefficients to derive enough number of relations expressed in Eq. (3). Fig. 5 shows the amount of  $\sum k_{V_{\text{thP}i}}^2$ ,  $\sum k_{V_{\text{thN}i}}^2$ , and  $\sum k_{L_i}^2$  as functions of supply voltages for a 19-stage inhomogeneous RO with an nMOS pass-transistor inserted inverter (NT-INV). As expected, the contribution of  $V_{\text{thN}}$  variability dominates over other components, especially in lower supply voltage. Similar dominance of  $V_{\text{thP}}$  variability can be seen in a pMOS pass-transistor inserted inhomogeneous RO.

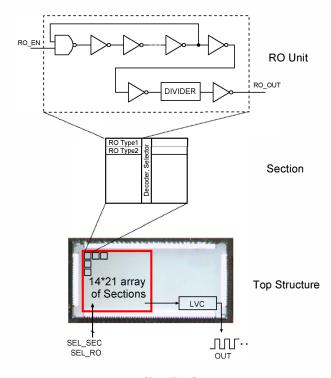

Fig. 6. 65nm Test Structure.

#### IV. 65nm Test Structure and Measurement Results

We have designed and fabricated an RO-array test structure that includes inhomogeneous ROs as well as homogeneous ROs in a 65nm process, and evaluate their variability. Through the measurement of WID frequency variation, we have extracted the amount of random variation in  $V_{\rm thN}$ ,  $V_{\rm thP}$ , and L. We also measured RTN-induced temporal variation of oscillation frequency in inhomogeneous RO.

## A. Test Structure

Fig. 6 shows an RO-array test structure fabricated in a 65nm process for measuring variability on real silicon. A "section" that contains various type of ROs is regularly placed in a 14-by-21 array, resulting 294 identical ROs on a chip. We can obtain WID frequency variation by measuring oscillation frequencies of identical ROs. Inhomogeneous ROs (Fig. 3(b),(c)) have been embedded in a section. A nominal supply voltage of the process is 1.2 V. A level converter (LVC in Fig. 6) is inserted between the test structure and a chip I/O for low voltage operation.

## B. Measurement Result

1) Extraction of WID random variability: We have measured the oscillation frequency of 294 ROs in each of homogeneous and inhomogeneous circuits for 15 chips. We thus have 4,410 measured frequencies for each RO type.

Fig. 7. Measurement result of WID variation in 1.2 V.

Fig. 8. Measurement result of WID variation in 0.8 V.

We normalized each measured frequency by the mean oscillation frequency of each chip.

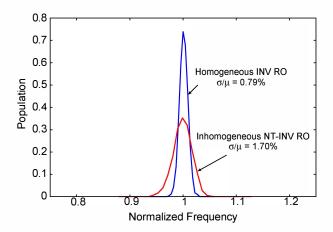

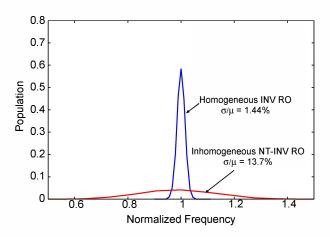

Figs. 7 and 8 show the distribution of oscillation frequencies of 19-stage homogeneous INV ROs and 19-stage nMOSFET-inserted inhomogeneous NT-INV ROs, at 1.2 V and 0.8 V, respectively. Oscillation frequencies are normalized by the mean oscillation frequency of each chip for eliminating the effect of D2D variation components. As expected, the inhomogeneous RO exhibit larger frequency spread, especially in lower supply voltage. Standard deviations of the homogeneous INV RO are 0.79 % (1.2 V) and 1.44 % (0.8 V), whereas those of the inhomogeneous NT-INV RO are 1.70 % (1.2 V) and 13.7 % (0.8 V) which are 2.2 times (1.2 V) and 9.5 times (0.8V) larger than those of the homogeneous RO.

Next, we have derived the amount of variation for each WID variability component. First, we have extracted the

Fig. 9. Average of Measured and simulated frequencies of inhomogeneous ROs.

Fig. 11. Oscillation frequency over 10 s with little fluctuation at 0.8 V supply voltage (RO A in Fig. 13).

Fig. 10. Measured and extracted WID frequency variations in inhomogeneous ROs.

Fig. 12. Oscillation frequency over 10 s with binary fluctuation at 0.8 V supply voltage (RO B in Fig. 13).

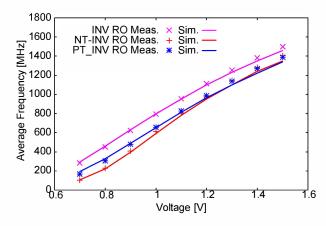

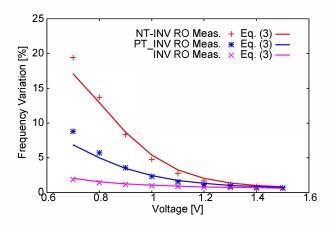

D2D components of  $V_{\rm thN}$ ,  $V_{\rm thP}$ , and L using homogeneous circuits of 13-stage INV ROs, 13-stage NT-INV ROs, and 13-stage PT-INV ROs on the same die, by the method described in Ref.[4]. The extracted parameters can reproduce the average frequency of inhomogeneous ROs on the same die by circuit simulation under the supply voltage from 0.7 V to 1.5 V. Fig. 9 shows the measured and simulated oscillation frequencies of homogeneous INV ROs, inhomogeneous NT-INV ROs, and inhomogeneous PT-INV ROs. The number of stages is 19 for all types of ROs, and the measured frequency is the average over 294 RO frequencies. They are in good agreement over the wide range of supply voltages.

With the extracted parameters, we have derived the sensitivity coefficients in Eq. (3) by circuit simulation. From the measured WID frequency variations of 19-stage homogeneous INV ROs, 19-stage inhomogeneous NT-INV

ROs, and 19-stage inhomogeneous PT-INV ROs, under the supply voltages from 0.7 V to 1.5 V, together with the derived sensitivity coefficients, we can obtain the standard deviations of  $V_{\text{thN}}$ ,  $V_{\text{thP}}$ , and  $L\left(\sigma_{V_{\text{thP}}}^2, \sigma_{V_{\text{thN}}}^2, \text{ and } \sigma_L^2\right)$  using Eq. (3). A least square method is used for the derivation. Extracted standard deviation of  $V_{\text{thP}}$  is 10 mV, that of  $V_{\text{thN}}$  is 17 mV, and that of L is 0.9 nm. The variation of  $V_{\text{thP}}$  and  $V_{\text{thN}}$  are close to those obtained by a device array[2], considering the difference in transistor width. Fig. 10 shows the measured and estimated WID frequency variations by Eq. (3).

2) RTN measurement: Inhomogeneous ROs can be used for the measurement of RTN-induced delay fluctuation[6][7].

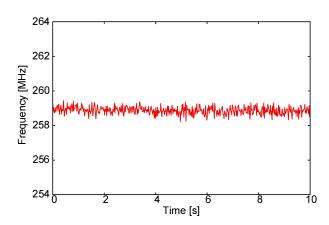

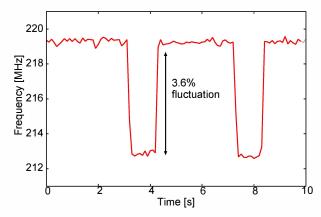

We have measured temporal variation of oscillation frequencies of 294 19-stage inhomogeneous NT-INV ROs on the same die at 0.8 V supply voltage. Oscillation

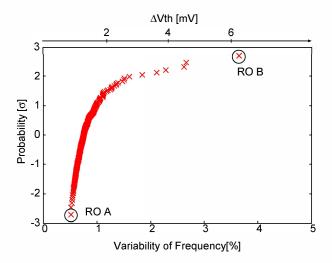

Fig. 13. CDF of RTN-induced frequency fluctuations.

frequencies are measured for every 20 ms over 10 s.

Two examples of the measured temporal frequency variations are shown in Figs. 11 and 12. Many ROs exhibit small amount of fluctuation similar to Fig. 11. However, we have observed a large amount of fluctuations in several ROs. In Fig. 12, a binary fluctuation of 3.6 % can be observed. Fig. 13 shows a cumulative distribution function (CDF) of all the frequency fluctuations over 294 ROs. The vertical axis of the CDF is in a log scale. Figs. 11 and 12 correspond to RO A and RO B in Fig. 13. The amount of frequency fluctuation can be converted into the fluctuation of threshold voltage using the sensitivity coefficient. The converted threshold voltage fluctuation is indicated on the top of Fig. 13. As pointed out in device-level researches such as Ref.[8], RTN does not have a Gaussian distribution, and a long tail exists for larger variability. With the use of inhomogeneous ROs, we can perform in-situ measurement of RTN under operation conditions. We were not able to observe RTN-induced variability in homogeneous ROs in the test structure.

#### V. Conclusion

In this paper, we have proposed an inhomogeneous RO that has small number of sensitive transistors. By inserting an nMOS/pMOS pass-transistor between the input and the gate of the nMOS/pMOS transistor of a single inverter in a homogeneous inverter RO, the sensitivity of the pass-transistor and the connected transistor becomes very much enhanced. Due to the dominant sensitivity, variability of the key transistor becomes visible in circuit operation, which can be used for variability characterization. We have measured WID variability and RTN using an RO-array test structure fabricated in a 65nm process, and reveal that proposed ROs are sensitive to WID local variability and

RTN. This structure is useful for accurate characterization of WID variability and RTN-induced variability.

#### ACKNOWLEDGMENT

The VLSI test chips in this study has been fabricated in the chip fabrication program of VDEC, the University of Tokyo in collaboration with STARC, e-Shuttle, Inc., and Fujitsu Ltd.

#### REFERENCES

- [1] A. Chandrakasan, D. Daly, D. Finchelstein, J. Kwong, Y. Ramadass, M. Sinangil, V. Sze, and N. Verma, "Technologies for ultradynamic voltage scaling," *Proceedings of the IEEE*, vol. 98, no. 2, pp. 191 –214, feb. 2010.

- [2] T. Tsunomura, A. Nishida, F. Yano, A. Putra, K. Takeuchi, S. Inaba, S. Kamohara, K. Terada, T. Hiramoto, and T. Mogami, "Analyses of 5-sigma Vth fluctuation in 65nm-MOSFETs using takeuchi plot," in VLSI Technology, 2008 Symposium on. IEEE, 2008, pp. 156–157.

- [3] H. Onodera and H. Terada, "Characterization of WID Delay Variability using RO-Array Test Structures," in *International Conference on ASIC*. IEEE, Oct. 2009, pp. 658–661.

- [4] I. Mahfuzul, A. Tsuchiya, K. Kobayashi, and H. Onodera, "Variation-sensitive monitor circuits for estimation of die-to-die process variation," in *Microelec*tronic Test Structures (ICMTS), 2011 IEEE International Conference on, april 2011, pp. 153 –157.

- [5] R. T.Sakurai, "Alpha-power law mosfet model and its applications to cmos inverter delay and other formulas," in *IEEE Journal of Solid-State Circuits*, 1990, pp. 584–594.

- [6] K. Ito, T. Matsumoto, S. Nishizawa, H. Sunagawa, K. Kobayashi, and H. Onodera, "The Impact of RTN on Performance Fluctuation in CMOS Logic Circuits," in *IEEE International Reliability Physics Symposium* (IRPS) 2011, 2011, pp. 710–713.

- [7] K. Ito, T. Matsumoto, H. Sunagawa, S. Nishizawa, K. Kobayashi, and H. Onodera, "Modeling of Random Telegraph Noise under Circuit Operation - Simulation and Measurement of RTN-induced delay fluctuation -," in *International Symposium on Quality Electronic Design (ISQED)*, 2011, pp. 22–27.

- [8] N. Tega, H. Miki, F. Pagette, D. Frank, A. Ray, M. Rooks, W. Haensch, and K. Torii, "Increasing threshold voltage variation due to random telegraph noise in fets as gate lengths scale to 20 nm," in VLSI Technology, 2009 Symposium on, june 2009, pp. 50 –51.