# Programmable Neuron Array Based on a 2-Transistor Multiplier Using Organic Floating-Gate for Intelligent Sensors

A. K. M. Mahfuzul Islam, *Member, IEEE*, Masamune Hamamatsu, Tomoyuki Yokota, Sunghoon Lee, *Member, IEEE*, Wakako Yukita, *Member, IEEE*, Makoto Takamiya, *Senior Member, IEEE*, Takao Someya, *Member, IEEE*, and Takayasu Sakurai, *Fellow, IEEE*

Abstract-Artificial neurons are introduced for local data processing in a large area sensor device, thereby reducing multiple sensor outputs to 1-bit digital output. To reduce the area overhead and layout complexity due to the artificial neuron array, a 2-transistor multiplier using organic floating-gate pFET is proposed. Each artificial neuron has multiple organic floatinggate pFETs embedded in it. A virtual scalable floating-gate based memory architecture is realized for selective programming of each floating-gate pFET. Threshold voltage tuning is utilized to realize both of the positive and the negative weight values for a neuron. A flexible interface pressure monitoring device with pressure-sensitive rubber sheet is developed for pressure ulcer prevention to show the feasibility of our concept. A 50 mm<sup>2</sup> organic sheet integrating 2×2 neuron array is fabricated with 2-V organic CMOS transistors. Selective floating-gate programming and neuron operation are successfully demonstrated.

Index Terms—Organic thin film transistor, floating-gate memory, artificial neuron, local signal processing, flexible sensor sheet, pressure sensor, analog filter.

### I. INTRODUCTION

ITH the emergence of Internet of Things (IoT) era, more and more physical objects are being connected to the internet. These IoT devices, which in most cases include sensors, provides information of our surrounding to enable a more secure and comfortable life. In order to gather information from the physical world, various forms of devices are required including devices capable of sensing large area. Especially for health-care and bio-medical applications, flexible and large area devices that can be attached to human skin for example will provide greater options.

For flexible and large area sensor applications, thin-film transistors using semiconductor materials such as organic [1], IGZO [2] and amorphous silicon [3] have shown promise to fulfill the above needs. However, in the literature, the

Manuscript received May 24, 2016; revised August 19, 2016; accepted September 23, 2016. This paper was recommended by Guest Editor J. S. Chang.

A. K. M. M. Islam, M. Takamiya, and T. Sakurai are with the Department of Informatics and Electronics, Institute of Industrial Science, The University of Tokyo, Tokyo 153-8505, Japan (e-mail: mahfuzul@iis.u-tokyo.ac.jp).

M. Hamamatsu, T. Yokota, S. Lee, W. Yukita, and T. Someya are with the Department of Electrical Engineering and Information Systems, School of Engineering, The University of Tokyo, Tokyo 113-8656, Japan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JETCAS.2016.2628411

transistors have been primarily used as switches in a large sensor array. Sensor applications have been reported integrating on-sheet amplifiers, ring oscillators, flip-flops etc. [4]–[9]. However, the existing sensor array based applications suffer from the following limitations:

- 1) large number of wires for read out;

- analog signals through long wires causing signal integrity problem; and/or

- 3) post-processing using computers for extracting the insights from the data.

Therefore, built-in local signal processing capability will broaden the use of sensor devices for large area monitoring. Although some functional circuits such as a microprocessor [10], transconductance amplifiers [6] or integration between flexible electronics and CMOS IC [11] have been reported, the integration with sensor array is not studied. In this paper, we propose a new sensor array architecture where local signal processing units are embedded into the sensor array to extract the essence of the sensed data and then output digital signals. Local processing reduces the number of wires significantly, thus ensures scalability of large area implementation. Digital output removes signal integrity problem.

In this paper, we show that artificial neuron can be used as a local signal processing unit. We propose a CMOS based compact 2-transistor (2T) multiplier using organic floating-gate pFET to realize an artificial neuron circuit with small transistor count. Transistor count is critical as there is limitation in metal layer resources for organic circuits. Floating-gate devices have been successfully demonstrated in [12], [13]. Researchers are developing systems that utilizes the precious floating-gate memories. One such example is an image classifier application where the floating-gate memories are used for storing weight values [13]. Floating-gate can also be used for post-fabrication tuning to encounter device variation [14]. One challenge for floating-gate memory based sensor array with local functional units is to find a way to program the floating-gate devices individually, Our proposed CMOS based multiplier scheme allows us to access the three terminal of a floating-gate device, hence implementation of a virtual memory array becomes possible.

To show the feasibility and application of the proposed system, we develop a flexible interface pressure monitoring system targeting pressure ulcer prevention. We demonstrate the application of artificial neurons for extracting real-time essence of sensor data. For example, non-uniform pressure distribution and local high pressure due to the wrinkles of clothes or bed sheet increase the rate of pressure ulcer, therefore early detection of the pressure non-uniformity is helpful. Uneven interface pressure distribution is one of the major causes for pressure ulcer development besides the high intensity pressure applied over a long period of time [15]. Constant monitoring of interface pressure can be useful in reducing the risk of pressure ulcer development. However, the conventional pressure mapping systems require external monitoring devices for image processing [16], [17]. Furthermore, as the monitored signals are analog, signal integrity is a problem to accurately capture the pressure readings. In order to overcome the above problems, we propose an intelligent pressure monitoring system that processes the analog pressure signals locally and output digital signals when an anomaly is found. The proposed intelligent system thus have the following advantages:

- 1) reduce the number of external wires;

- 2) digital output provides robust data transmission;

- 3) constant monitoring without human intervention by warning the anomaly; and

- 4) programmability for adaption based on target patient.

In this paper, the world's first artificial neuron using OFETs is proposed for local signal processing. A flexible pressure monitoring device integrating  $2 \times 2$  artificial neurons is demonstrated. The key contributions of this paper are as follows:

- 1) propose a 2-transistor multiplier topology;

- 2) demonstrate artificial neuron operation that utilizes the 2T multiplier;

- 3) develop scalable neuron array architecture for local processing and digital output; and

- 4) scalable virtual floating-gate memory array with programming scheme.

The remainder of the paper is organized as follows. We describe the pressure monitoring system and its components in Section II. In Section III, an artificial neuron topology utilizing a new 2-transistor multiplier topology is proposed. In Section IV, several experimental results will be discussed to show the feasibility of the proposed system. Section V concludes the paper.

# II. INTELLIGENT PRESSURE MONITORING SYSTEM

In this section, we develop a flexible pressure monitoring system with built-in analog filters and digital output. First, the system overview is described to show how the transistors and sensors are integrated. Then, we introduce the use of artificial neuron topology as an analog filter with small area foot print.

## A. System Overview

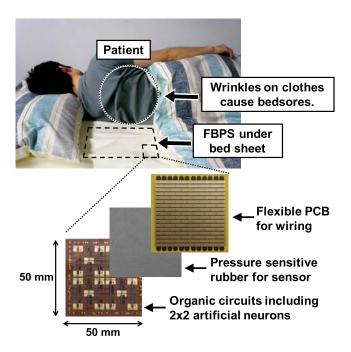

Fig. 1 shows a photo of the developed pressure monitoring device. The device can be placed under the bed sheet to measure the pressure distribution. The system shown in Fig. 1 features local on-sheet analog signal processing for digital output. In the system, three flexible sheets are stacked and laminated together. The three sheets consist of a flexible PCB (Printed Circuit Board), a pressure-sensitive rubber sheet [12], and a plastic sheet with printed organic circuits. The rubber

Fig. 1. Example of a flexible pressure monitoring system for pressure ulcer prevention. Three flexible sheets including a PCB, a pressure-sensitive rubber sheet and an organic circuit sheet are stacked together.

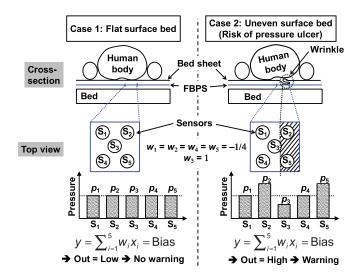

Fig. 2. An example of non-uniform pressure distribution because of uneven surface. Artificial neuron can be used to detect the non-uniform distribution.

sheet is sandwiched between the organic sheet and PCB sheet. The purpose of the PCB sheet is to supply a uniform bias voltage to one side of the rubber sheet. In fact, the PCB sheet can be replaced by any conductive sheet that is flexible. The three sheets can be sticked together with adhessive systems such as silver paste or anisotropic conductive film bonding. In [18], integration of organic sheet and rubbery sensor sheet to form flexible touch sensor device is demonstrated. We adopt the above approach to realize pressure sensor device. The PCB sheet applies a bias voltage to the rubber sheet on one surface uniformly. The organic transistors receive pressure signals from the rubber sheet through contact pads.

The operation of the proposed device is shown in Fig. 2 where two cases of pressure distributions are illustrated. In the

TABLE I

COMPARISON BETWEEN ORGANIC FET AND SILICON MOSFET

|                        | Organic FET        | Silicon MOSFET |

|------------------------|--------------------|----------------|

| Minimum gate length    | $20~\mu\mathrm{m}$ | 22 nm          |

| Mechanical flexibility | Flexible           | Very limited   |

| Normalized ON current  | 50 nA /μm @ 2V     | 1 mA/μm @ 1V   |

| Gate delay             | 10 ms @ 2V         | 10 ps @ 1V     |

| Cost / area            | Low                | High           |

| Cost / transistor      | High               | Low            |

| Lifetime               | Months             | Years          |

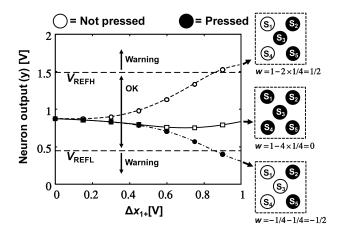

first case, uniform pressures are applied to the interface, In the second case, non-uniform pressures are applied. We need a circuit to detect the non-uniformity and warn with a digital signal. As shown in the figure, this can be achieved by an analog filter. In this example, non-uniformity can occur from any direction. Weight assignment in an artificial neuron consisting of five sensors of  $w_1 = w_2 = w_4 = w_5 = -1/4$  and  $w_3 = 1$  will realize such a filter. On a flat surface bed, the pressures on  $S_1$ – $S_5$  are the same, and "Out" is low showing "No warning". In contrast, on an uneven surface bed, the pressures on  $S_1$ – $S_5$  are different, and "Out" is high showing "Warning".

### B. Sensor Material

For any sensor application design, the choice of sensor material plays an important role. Pressure can be sensed by measuring the capacitance or the resistance between the two surfaces in between where the pressure is applied. In [17], a capacitive pressure sensor has been demonstrated. However, capacitive sensors suffer from integration complexity as dielectric materials and electrodes need to be integrated. Another example of pressure sensor is to use polymeric piezoelectric [polyvinylidene difluoride (PVDF)] sheet. In this case intermolecular polarization mechanism is used to generate small signals. However, as the signal is small, amplifiers are required that may add additional complexity to the system. Pressure-sensitive rubber has been successfully demonstrated in [12] and [18]. In this paper, we adopt a pressure-sensitive rubber approach because of high sensitivity and ease of integration. In the rubber sheet, when mechanical pressure is applied in lateral direction to the sheet, the resistance between the surfaces increases. Thus, the rubber sheet can be seen as variable resistor whose resistance varies depending on the applied pressure. The sensor resistance will then be converted to voltage levels so that the transistors can process the signals.

# C. Organic Transistors and Floating-gate Devices

For biomedical and healthcare applications, large area sensing and low voltage operation is preferable. In order to understand the organic transistors and their usage, we show a comparison between organic material based FET and silicon MOSFET in Table I. Silicon MOSFETs have very high drivability and can be integrated in large number in a very small area. Thus they are suitable high performance computing. However, they are not suitable for large area as cost per area becomes high. On the other hand, cost per area is low for

organic FETs. Furthermore, organic FETs provide flexibility and transparency which the silicon counterpart cannot provide. But, a key point here is that although cost per area is low for organic FETs, cost per transistor is actually very high for organic FETs. Thus, using organic FETs in small numbers is an imortant key. Another feautre of organic FET based devices is that the devices are printed on a sheet, thus there are limitations on the number of metal layers that can be used for interconnect. Based on the above limitations, circuit topologies need to be adopted to utilize the organic FETs to pave the way for new applications.

Organic transistors are also shown to be operable under 2 V [4], [12]. Self-assembled monolayer (SAM) technology is used to form very thin dielectric layer allowing low voltage operation. We use a similar technology for our demonstration in this paper. The organic semiconductors used for p-type and n-type transistors are DNTT [19] and PDI-8CN2 [20], respectively. The floating-gate in a pFET can be programmed with gate-source voltage of -6 V to -4 V and erased with gate-source voltage of +3 V. We have fabricated organic transistors and floating-gate pFETs with gate length of 50  $\mu$ m. The organic sheet consists of one metal layer for transistor gate, one metal layer for source and drain, and one layer for contact pads. Through hole vias are used for connecting the three metal layers. Thanks to the small transistor count, the neuron array is designed with just two metal layers for interconnect.

# D. Local Processing for Pattern Extraction

In large-scale real-time sensor application, the essence of the data is important for decision making. The proposed system locally detects the uneven pressure distributions and warn us only when the unevenness crosses a certain threshold. For such an application, the following problems need to be addressed. First, the patient weights differ largely such that the amount of pressure is different from patient to patient. Second, threshold for detecting the unevenness is not a universal value. Therefore, a system with post-fabrication capability of tuning the threshold and pressure sensitivity can be very helpful. Programming of the floating-gate memory provides the above capability.

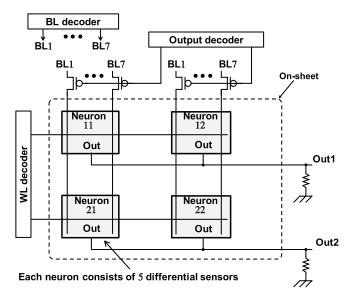

Fig. 3 shows the block diagram of the proposed architecture. An array of artificial neurons are implemented on the organic sheet. Each neuron outputs a digital signal based on the interface pressure distribution. Word line and bit line decoders provide appropriate signals to the system for selective floatinggate programming. The bit lines are shared among the columns where each column is activated by an output decoder. During the read-out phase, the bit lines are set to the supply voltage and the output decoder selects a particular neuron column. During the programming phase, the bit line and word line voltages are tuned to program the threshold voltages. Only the neurons in the selected column drive the output lines as neurons under other columns are deactivated. The number of output wires for an  $N \times N$  neuron array is only N. In this demonstration, each neuron consists of five sensor inputs. Thus, the number of output wires for each neuron is reduced from 5 to 1. In a conventional approach based on a sensor

Fig. 3. Scalable neuron array for on-sheet filtering with digital output. Each neuron block corresponds to the schematic shown in Fig. 12.

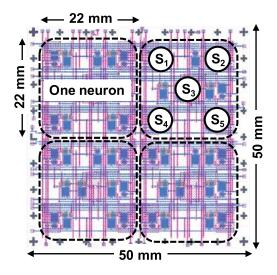

Fig. 4. Layout of an 2x2 neuron array built on an organic transistor sheet.

matrix, analog signal outputs are read through long wires. Whereas, the proposed system output digital signals.

# E. Organic Sheet Layout

Fig. 4 shows the layout of a designed  $2 \times 2$  neuron array on a plastic sheet. The size of each neuron is  $22 \times 22$  mm<sup>2</sup> where five sensors are embedded. Thanks to the organic transistors and the proposed 2-transistor multiplier based neuron circuit, high spatial resolution of 1.03 sensors/cm<sup>2</sup> is achieved compared with 0.264 sensors/cm<sup>2</sup> with a capacitance sensor [17]. The operation mechanism of the neuron circuit will be discussed in the next section.

## III. ARTIFICIAL NEURON AS ANALOG FILTER

The heart of the proposed intelligent sensor system is the neuron circuit with small transistor counts. The small

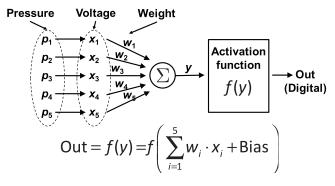

Fig. 5. Artificial neuron as analog filter for local signal processing.

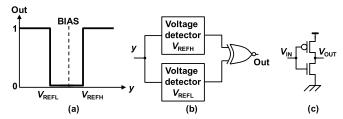

Fig. 6. Activation function for digitization.

transistor count is achieved by developing a new 2-transistor multiplier topology that utilizes threshold voltage tuning by the floating-gate. In this section, we describe the artificial neuron architecture, its usage as analog filter and the 2-transistor multiplier topology.

### A. Artificial Neuron

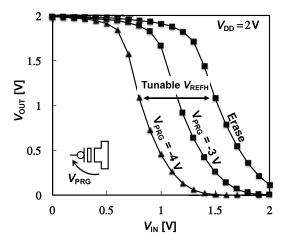

Fig. 5 shows an artificial neuron example for five pressure inputs. Fig. 6 illustrates the activation function. Fig. 6(c) shows a CMOS inverter with floating-gate pFET as the voltage detector. By changing the threshold voltage of the floating-gate pFET, the logical threshold voltage of CMOS inverter is programmed, thereby programmable threshold voltages ( $V_{\rm REFH}$ ,  $V_{\rm REFL}$ ) are achieved.

## B. 2-Transistor Multiplier

Analog multiplier based on neuron-FET or differential circuit techniques are proposed [21]–[23]. However, both of them require analog voltages as weights. Other multiplier techniques such as capacitance tuning for learning is reported [24]. [13] proposes a 4-transistor multiplier utilizing floating-gate devices for classifier implementation. Here, we propose a 2T topology.

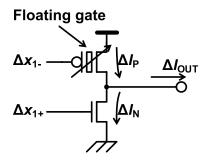

Fig. 7 shows the proposed 2-transistor multiplier using an organic floating-gate pFET. The multiplier is a CMOS circuit with a p-type FET and a n-type FET. Compared with a previously reported 4-transistor multiplier [13], the number of transistors is reduced by half. The input voltages  $(\Delta x_{1+}, \Delta x_{1-})$  are differential. The operation of the multiplier is explained using a square-power law model for the FET ON current. First, the ON current change of an OFET is expressed as follows:

$$\Delta I_{\rm DS} = \beta \left( \Delta V_{\rm GS} - V_{\rm TH} \right)^2, \tag{1}$$

Fig. 7. A 2T multiplier cell with differential input and single-ended output.

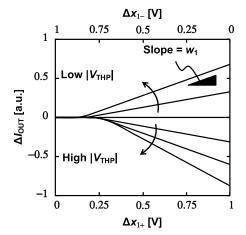

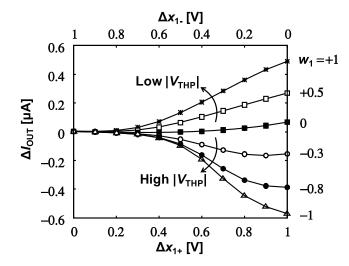

Fig. 8. Simulated  $\Delta I_{\rm OUT}$  of the 2T multiplier for different  $V_{\rm THP}$  values. Both of the positive and the negative weights are realized by tuning the  $V_{\rm THP}$  value.

where  $\beta = \mu C_{\rm OX}(W/L)$ .  $\Delta I_{\rm OUT}$  is calculated as follows:

$$\Delta I_{\text{OUT}} = \Delta I_{\text{DS,P}} - \Delta I_{\text{DS,N}},$$

$$= 2\beta_{\text{N}} (1 - m \cdot k \cdot n) V_{\text{THN}} \cdot \Delta V_{\text{GSN}}$$

$$+ \beta_{\text{N}} (m \cdot k^2 - 1) \cdot \Delta V_{\text{GSN}}^2$$

$$+ \beta_{\text{N}} (m \cdot n^2 - 1) \cdot V_{\text{THN}}^2. \tag{2}$$

Here,

$$m = \frac{\beta_{\rm P}}{\beta_{\rm N}}, n = \frac{|V_{\rm THP}|}{V_{\rm THN}}, k = \frac{\Delta |V_{\rm GSP}|}{\Delta V_{\rm GSN}}$$

(3)

$V_{\rm THP}$  and  $V_{\rm THN}$  are threshold voltages of the pFET and nFET respectively. When, m=k=1, and  $\Delta V_{\rm GSN}=\Delta x_{1+}$ , we obtain

$$\Delta I_{\text{OUT}} = 2\beta_{\text{N}} \cdot (V_{\text{THN}} - |V_{\text{THP}}|) \cdot \Delta x_{1+} + \theta, \qquad (4)$$

$$=2\beta_{\rm N}V_{\rm THN}\cdot(1-n)\cdot\Delta x_{1+}+\theta. \tag{5}$$

Here,  $\theta = \beta_{\rm N} \cdot (n^2 - 1) \cdot V_{\rm THN}^2$ . In (5),  $\Delta I_{\rm OUT}$  is a product of the threshold voltage difference and the gate voltage change, hence realizes the multiplier. The term  $\theta$  does not depend on the gate voltage change, thus is treated as a constant.  $2\beta_{\rm N} \cdot (V_{\rm THN} - |V_{\rm THP}|)$  can be utilized as a variable weight for the artificial neuron. Both positive and negative weight are realized by tuning  $V_{\rm THP}$  of the floating-gate pFET.

Fig. 8 shows the simulated  $\Delta I_{\rm OUT}$  for the 2T multiplier considering the ideal square-power law model for the OFET I-V characteristic. When  $|V_{\rm THP}|$  is lower than  $V_{\rm THN}$ ,  $\Delta I_{\rm OUT}$

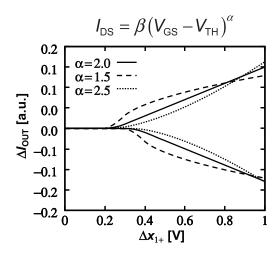

Fig. 9. Simulated  $\Delta I_{\rm OUT}$  of the 2T multiplier for different values of  $\alpha$  in the  $\alpha$ -power law model of transistor ON current.

increases with the increase of nFET gate voltage increase. Whereas, when  $|V_{\text{THP}}|$  is higher than  $V_{\text{THN}}$ ,  $\Delta I_{\text{OUT}}$  decreases. The value of  $V_{\text{THP}}$  determines the gradient of  $\Delta I_{\text{OUT}}$  thereby realizes different weight values.

In reality, the transistor ON current may not follow the ideal square-power law model. Considering velocity saturation and other mobility degradation phenomena, the  $\alpha$ -power law model is proposed to model the ON current [25]

$$I_{\rm DS} = \beta \left( V_{\rm GS} - V_{\rm TH} \right)^{\alpha}. \tag{6}$$

The detailed dc modeling of organic transistors are described in [26], [27]. From the above studies, the value of  $\alpha$  may differ from the ideal square-power model. However, we show that even if the  $\alpha$  value varies from the square, the multiplier operation is still achieved. Fig. 9 shows the  $\Delta I_{\rm OUT}$  change for three different values of 2.0, 1.5, and 2.5. Deviation from the ideal square-power model introduces some non-linearity, but the multiplier and variable weight characteristics exist. Thus, we conclude that the multiplier can be used as an analog filter in those cases too.

Next, we discuss on the resolution of weight tuning by  $V_{\text{THP}}$  programming. The weight, w, is represented as follows from (5)

$$w = 2\beta_{\rm N} V_{\rm THN} \cdot (1 - n). \tag{7}$$

Here, n is defined as  $|V_{\rm THP}|/V_{\rm THN}$ . In order to realize normalized weight values of +1 and -1, the values of n need be set to 0.5 and 1.5. These values refer that  $V_{\rm THP}$  need to tuned to the half of  $V_{\rm THN}$  for +1 weight, and 1.5 times higher than  $V_{\rm THN}$  for -1 weight. For example, For a  $V_{\rm THN}$  value of 500 mV,  $V_{\rm THP}$  need to be set at 250 mV for +1 weight, and 750 mV for -1 weight. The range of  $V_{\rm THP}$  tuning is 500 mV. Thus, a  $V_{\rm THP}$  tuning precision of 50 mV will give us a 10% tuning capability of the weights when  $V_{\rm THN}$  is 500 mV. The impact of device variability and performance degradation over time need also be taken into account. As will be shown in Section IV, device variability can be overcome by programming the devices. However, device degradation can pose a challenge. Device degradation will reduce the

Fig. 10. Two different circuit topologies as sensor to voltage converter to generate differential voltages.

Fig. 11. Cross section of the three layers consisting of flexible PCB for bias electrode, rubber sheet for as pressure sensors and organic sheet for signal processing.

weight resolution capability. In such case, only coarse tuning of weight values might be feasible.

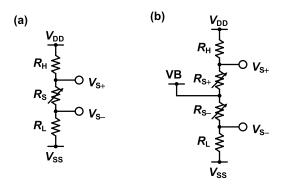

# C. Sensor to Voltage Converter

To implement the proposed multiplier based artificial neuron, we need to generate differential input for the multiplier. Differential voltages can be generated using the two converter topologies shown in Fig. 10. For the topology in Fig. 10(a), the differential voltage,  $\Delta V_S$ , is expressed as follows:

$$V_{S+} = \frac{R_S + R_L}{R_H + R_S + R_L} \cdot (V_{DD} - V_{SS}), \tag{8}$$

$$V_{S-} = \frac{R_{L}}{R_{H} + R_{S} + R_{L}} \cdot (V_{DD} - V_{SS}), \tag{9}$$

$$\Delta V_{\rm S} = \frac{R_{\rm S}}{R_{\rm H} + R_{\rm S} + R_{\rm L}} \cdot (V_{\rm DD} - V_{\rm SS}). \tag{10}$$

$\Delta V_{\rm S}$  is a function of  $R_{\rm S}$ .  $R_H$  and  $R_L$  are chosen considering the required voltage sensitivity and voltage range.

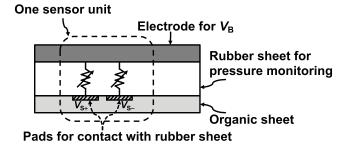

The topology of Fig. 10(a) can be realized when the sensor is on the same sheet as the FETs. However, often the sensors are implemented in different sheets as is the case with our target application. We develop a converter topology shown in Fig. 10(b) to generate differential inputs. In this topology, two sensors closely placed with each other are utilized. Fig. 11 shows a cross-section view of the three stacked sheets to illustrate the feature. In this case, one sensor unit consists of two current paths in the rubber sheet. Two contact pads in the organic sheet is placed closely such that they receive similar pressure signals. The sensor output voltages then are

expressed as follows:

$$V_{S+} = \frac{R_{S+}}{R_{H} + R_{S+}} \cdot \frac{(V_{DD} - V_{SS})}{2},$$

(11)

$$V_{\rm S-} = \frac{R_{\rm L}}{R_{\rm L} + R_{\rm S-}} \cdot \frac{(V_{\rm DD} - V_{\rm SS})}{2}.$$

(12)

When,  $V_{\rm B}=(V_{\rm DD}-V_{\rm SS})/2$ ,  $R_{\rm H}=R_{\rm L}=R_{\rm B}$ , and  $R_{\rm S+}=R_{\rm S-}$ , the differential voltage becomes as follows:

$$\Delta V_{\rm S} = \left(1 - \frac{2R_{\rm B}}{R_{\rm B} + R_{\rm S}}\right) \cdot \frac{(V_{\rm DD} - V_{\rm SS})}{2}.$$

(13)

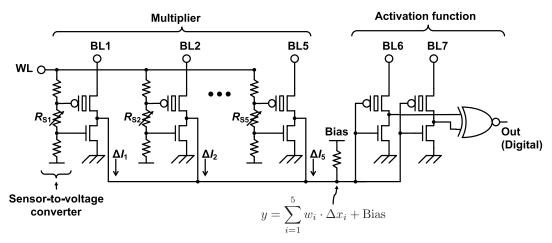

### D. Artificial Neuron With Activation Circuit

Fig. 12 shows the complete schematic of an artificial neuron with activation circuit. The neuron consists of five multipliers. Each multiplier receives differential inputs from the rubber sensor. The multiplier outputs are connected together. The currents from the multipliers are summed though the resistor  $R_{\rm OUT}$ . A Bias voltage is applied for the bias setting. This bias voltage is global to the entire sheet. The activation circuit consists of two variable threshold inverters and a NOR gate. If the neuron output is between  $V_{\rm REFH}$  and  $V_{\rm REFL}$ , the circuit output is LOW. Otherwise, the output is HIGH meaning anomaly is detected.

During read operation, WL and BLs are same as  $V_{\rm DD}$ . During programming, WL selects the target neuron and BLs select a target floating-gate pFET. By providing appropriate voltage levels to the WL and BL signals, selective programming of each floating-gate is achieved.

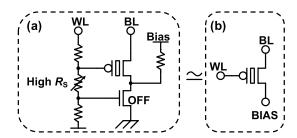

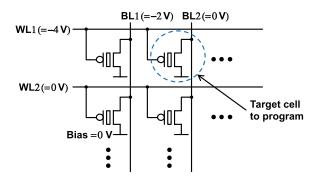

### E. Scalable Memory Array

In order to realize a scalable memory array embedded in an array of neurons, access to all three terminals of a floating-gate device is required. Fig. 13(a) shows a 2T multiplier with sensor-to-voltage converter circuits. During writing and erasing operation, the n-type OFET is turned OFF and the sensor resistance is very high. As a result, Fig. 13(a) circuit is equivalent to the circuit in Fig. 13. The bias voltage is common for all the multipliers. Thanks to the CMOS based 2T multiplier circuit, a virtual memory array as shown in Fig. 14 can be realized. By appropriately choosing the voltage levels for the word lines and bit lines, each floating-gate device can be programmed selectively. The required voltage configurations to write a particular floating-gate is also shown in the figure. The experimental validation of the configurations will be demonstrated in Section IV.

# IV. EXPERIMENTAL RESULTS

In this section, we demonstrate the feasibility of our proposed system. We show the measurement results for each of the circuit components first. Then, neuron functionality for three different pressure conditions will be demonstrated.

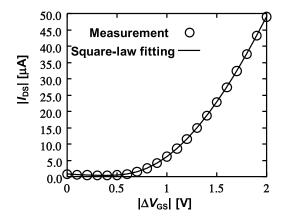

# A. Transistor I-V Characteristics

The transistor I-V characteristics are demonstrated first. The measured  $I_{\rm DS}-V_{\rm GS}$  of our fabricated p-type OFET is shown in Fig. 15. Square-power law model fitting is also

Fig. 12. Complete neuron schematic with programmable activation circuit. Output currents of the five multipliers are summed together.

Fig. 13. Equivalent circuit to control floating-gate device terminals for selective writing and erasing.

Fig. 14. Virtual floating-gate based memory array realized.

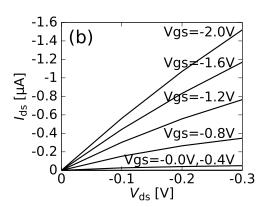

shown in the figure. The square-power law model fits the  $I_{\rm DS}-V_{\rm GS}$  well. Next, the resistors in the system are realized by OFETs operating in small  $V_{\rm DS}$  range. Fig. 16 shows the measured  $I_{\rm DS}-V_{\rm DS}$  under constant  $V_{\rm GS}$ .  $I_{\rm DS}$  changes linearly with  $V_{\rm DS}$  change.

# B. Multiplier Operation

Next, we demonstrate our proposed 2T multiplier which is the backbone of the whole system. Fig. 17 shows the measured  $\Delta I_{\rm OUT}$  of the multiplier cell against the differential input voltage changes. The lower X-axis shows the applied input voltage to the nFET gate and the upper X-axis shows the input voltage to the pFET gate. Y-axis shows the current difference between the pFET and the nFET. By tuning the pFET threshold voltage,  $V_{\rm THP}$ , the output current  $\Delta I_{\rm OUT}$  either increases or decreases depending on the  $V_{\rm THP}$  values.

Fig. 15. Measured organic pFET  $\Delta I_{DS}$ - $\Delta V_{GS}$  characteristic.

Fig. 16. Organic pFET  $\Delta I_{DS}$ - $V_{DS}$  characteristics.

When  $|V_{\text{THP}}|$  is low,  $I_{\text{OUT}}$  increases according the differential input increase. Whereas, when  $|V_{\text{THP}}|$  is high,  $I_{\text{OUT}}$  decreases. The tangent of  $I_{\text{OUT}}$  differs which is utilized here to realize different weights. Both of the positive and negative weights are realized by  $V_{\text{THP}}$  tuning which are key characteristics for implementing analog filters.

## C. Variable Threshold Inverter

Fig. 18 shows the measured voltage transfer characteristics of an inverter with a floating-gate pFET. The initial logic

Fig. 17.  $\Delta I_{\rm OUT}$  versus gate bias change for a 2T multiplier cell.

Fig. 18. Variable threshold inverter realized by floating-gate pMOS memory.

threshold before programming is around 1.6 V. Then, programming is performed by applying -3 V and -4 V between gate and source for 1 s. When programmed with -3 V, the logic threshold shifts to around 1.2 V. When programmed with -4 V after erasing the floating-gate to its initial state, the logic threshold shifts to around 0.8 V. The erase operation is performed with +3 V. The amount of threshold programming is controlled by the bias voltage and bias time [12]. Thanks to the floating-gate, a wide range of threshold values can be realized. The gain in Fig. 18 is relative low. However, it is reported that by adopting a pseudo-CMOS topology for OFETs, inverter gain can be improved significantly [4], [28].

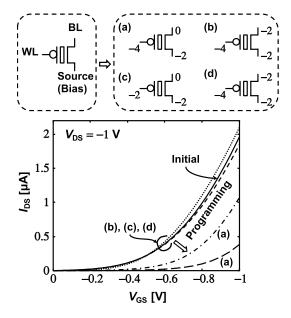

## D. Floating-Gate Programming for Scalable Array

In order to realize a scalable memory array based on organic floating-gate device, bias configurations enabling selective writing and erasing are required. As already explained in [12], gate—source voltage of -3 V or above is required to tune threshold voltage of a floating-gate pFET. Utilizing this key characteristic, we develop a scalable memory array with world lines and bit lines to selectively program floating-gate devices. For an  $n \times n$  memory array, word and bit line based array

Fig. 19. Selective writing demonstration of a floating gate device in an array.

architecture reduces the number of wires from  $n^2$  to  $2 \times n$  compared with an one dimensional implementation.

Fig. 19 shows the I-V characteristics of a floating-gate pFET after four different bias configurations are applied for 1 s. The four bias configurations are shown in Fig. 19(a)–(d). With Fig. 19(a) bias conditions, gate–source voltage of -4 Vis applied. As a result, the transistor  $V_{\text{TH}}$  is increased. In the plot, one curve correspond to the initial state, and two curves correspond to when -4 V is applied. Fig. 19(a) configuration is applied twice without any erase operation in between. Incremental increase in the threshold value is observed when Fig. 19(a) configuration is applied successively. Thus, as reported in [12], both the programming voltage and the programming time can use used to tune the threshold voltage. Adaptive tuning of programming voltage and programming time based on the transistor ON current reading can ensure that the target threshold voltage is achieved. Adaptive programming also has the benefit of compensating transistor to transistor variability. For the other three bias configurations, transistor I-V characteristic remains the same.

Fig. 20 shows the measured I-V characteristics of a floating-gate pFET when erasing is performed. Fig. 20(a)–(d) shows four different bias configurations. Floating-gate is erased only with the Fig. 20(a) configuration which confirms that selective erasing can be performed by tuning the bias voltages.

## E. Neuron Operation

We demonstrate the feasibility of the artificial neuron operation. We apply indepenent analog voltages to each sensor pads externally instead of applying pressure on the rubber sheet. If the supply voltage and the bias voltage is set to 2 V and 1 V respectively, then the input voltage range of the sensor pads connected to pFET is  $1\sim 2$  V. The input voltage range of the sensor pads connected to nFETs is  $0\sim 1$  V. Gate voltages of pFETs and nFETs change in opposite direction according

Fig. 20. Selective erasing demonstration of a floating gate device in an array.

Fig. 21. System demonstration with three different pressure profiles.

to the applied pressure. Thus, gate bias voltage relationship can be represented by

$$\Delta x_{1-} = V_{\rm DD} - \Delta x_{1+},\tag{14}$$

where  $\Delta x_{1+}$  represents nFET's gate voltage and  $\Delta x_{1-}$  represents pFET's gate voltage change. For simplicity, we assume that all sensors that are pressed receive the same pressure resulting in the same gate voltages.

Fig. 21 shows the neuron operation for three different scenarios. X-axis shows the change of applied gate voltage to the nFET. pFET gate voltage is applied according to (14). In the first scenario, all the sensors are assumed to have same values meaning there is no unevenness in the surface. In the second scenario, only sensors  $S_2$  and  $S_5$  are assumed to have pressures applied. In the third scenario, sensors  $S_2$ ,  $S_3$  and  $S_5$  are assumed to have pressures applied. For the first case, as there is no unevenness and because of the weight assignments, the output voltage does not change much and remains within  $V_{\text{REFH}}$  and  $V_{\text{REFL}}$ . For the other two scenarios that represent uneven pressure distributions, the output voltage

TABLE II Comparison With State-of-the-Art

|                           | Conv. [8]           | This work           |

|---------------------------|---------------------|---------------------|

| Analog<br>multiplier      |                     | V <sub>s</sub> =    |

| Transistor count          | 4 –50               | 2                   |

| Non-volatile memory count | 2 _50               | % 1                 |

| Scalable<br>memory array  | No                  | Yes                 |

| Technology                | a-Si TFT<br>nMOS    | Organic TFT<br>CMOS |

| Non-volatile device       | Charge trap<br>nMOS | Floating gate pMOS  |

| Program voltage           | 80 V 1/2            | 20 –4V              |

| Erase voltage             | −80 <b>V</b>        | +3 <b>V</b>         |

changes either to positive or to negative direction depending on the pressure distribution. Thus, the artificial neuron operation is confirmed.

## F. Comparison

Finally, we make a comparison of the proposed 2T multiplier with the one recently reported for implementing classifiers. Table II shows the comparison. The key differences are the transistor count and the number of floating-gate devices. Reducing the number of floating-gate devices and the multiplier transistor number to half is important here. The small transistor count reduces the system complexity and the number of wires required for programming. Furthermore, the CMOS based topology in our proposed multiplier enables access to the floating-gate terminals.

# V. Conclusions

Embedding analog filters on top of a sensor array for local signal processing is feasible. The local processing capability makes the device intelligent and reduces the data transmission by extracting the desired pattern in the sensed signals. Transistor count is critical for organic transistor based flexible sheets as the metal layer resources are very limited. An artificial neuron is developed to detect the non-uniform interface pressure distribution that utilizes a 2-transistor multiplier topology. The multiplier topology is a CMOS circuit that multiplies the threshold voltage difference and the gate-source voltage. Organic floating-gate pFET is used as a programmable memory to realize various weights for the neuron and variable threshold inverter. A virtual floating-gate memory array is realized where word line and bit line based program architecture is developed for scalability. Thus, a programmable neuron array is realized where each neuron outputs a digital signal depending on the sensed pressure distribution. As the output is digital, signal integrity problem is avoided.

The operation of the multiplier and the neuron is demonstrated with fabricated organic transistor sheet. Measurement results show the selective programming of each floating-gate memory although the floating-gate device is embedded in a neuron circuit thanks to the CMOS multiplier. The proposed system can pave the way for versatile and smart sensor devices with large-area flexible electronics.

### ACKNOWLEDGMENTS

The authors would like to thank Dr. H. Fuketa of National Institute of Advanced Industrial Science and Technology (AIST) for his advices in designing and measuring the organic transistor sheet.

### REFERENCES

- Z. Bao and J. Locklin, Organic Field-Effect Transistors. Boca Raton, FL, USA: CRC Press, 2007.

- [2] H. Yabuta et al., "High-mobility thin-film transistor with amorphous InGaZnO<sub>4</sub> channel fabricated by room temperature RF-magnetron sputtering," Appl. Phys. Lett., vol. 89, no. 11, 2006, Art. no. 112123.

- [3] A. Nathan, A. Kumar, K. Sakariya, P. Servati, S. Sambandan, and D. Striakhilev, "Amorphous silicon thin film transistor circuit integration for organic LED displays on glass and plastic," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1477–1486, Sep. 2004.

- [4] T. Yokota et al., "Sheet-type flexible organic active matrix amplifier system using pseudo-CMOS circuits with floating-gate structure," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3434–3441, Dec. 2012.

- [5] T. Zaki et al., "A 3.3 V 6-bit 100 kS/s current-steering digital-to-analog converter using organic p-type thin-film transistors on glass," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 292–300, Jan. 2012.

- [6] G. Maiellaro et al., "High-gain operational transconductance amplifiers in a printed complementary organic TFT technology on flexible foil," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 60, no. 12, pp. 3117–3125, Dec. 2013.

- [8] H. Fuketa et al., "Organic-transistor-based 2kV ESD-tolerant flexible wet sensor sheet for biomedical applications with wireless power and data transmission using 13.56 MHz magnetic resonance," in Proc. IEEE Int. Solid State Circuits Conf., Feb. 2014, pp. 490–491.

- [9] H. Fuketa et al., "Energy-autonomous fever alarm armband integrating fully flexible solar cells, piezoelectric speaker, temperature detector, and 12V organic complementary FET circuits," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 2015, pp. 1–3.

- [10] K. Myny, E. van Veenendaal, G. H. Gelinck, J. Genoe, W. Dehaene, and P. Heremans, "An 8-bit, 40-instructions-per-second organic micro-processor on plastic foil," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 284–291, Jan. 2012.

- [11] Y. Hu et al., "Large-scale sensing system combining large-area electronics and CMOS ICs for structural-health monitoring," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 513–523, Feb. 2014.

- [12] T. Sekitani et al., "Organic nonvolatile memory transistors for flexible sensor arrays," Science, vol. 326, no. 5959, pp. 1516–1519, 2009.

- [13] W. Rieutort-louis, T. Moy, Z. Wang, S. Wagner, J. C. Sturm, and N. Verma, "A large-area image sensing and detection system based on embedded thin-film classifiers," *IEEE J. Solid-State Circuits*, vol. 51, no. 1, pp. 281–290, Jan. 2015.

- [14] T.-C. Huang, K. Ishida, T. Sekitani, M. Takamiya, T. Someya, and T. Sakurai, "A floating-gate OTFT-driven AMOLED pixel circuit for variation and degradation compensation in large-sized flexible displays," in *Proc. Symp. Inf. Display (SID)*, Jun. 2011, pp. 149–152.

- [15] H. Wong et al., "Efficacy of a pressure-sensing mattress cover system for reducing interface pressure: Study protocol for a randomized controlled trial," *Trials*, vol. 16, no. 1, p. 434, 2015.

- [16] K. Sakai et al., "Continuous monitoring of interface pressure distribution in intensive care patients for pressure ulcer prevention," J. Adv. Nursing, vol. 65, no. 4, pp. 809–817, Apr. 2009.

- [17] M. Yip, D. D. He, E. Winokur, A. G. Balderrama, R. Sheridan, and H. Ma, "A flexible pressure monitoring system for pressure ulcer prevention," in *Proc. Annu. Int. Conf. IEEE Eng. Med. Biol. Soc.*, Sep. 2009, pp. 1212–1215.

- [18] T. Someya and T. Sakurai, "Integration of organic field-effect transistors and rubbery pressure sensors for artificial skin applications," in *Proc.* IEEE Int. Electron Devices Meeting, Dec. 2003, pp. 203–206.

- [19] U. Zschieschang et al., "Dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) thin-film transistors with improved performance and stability," Organic Electron., Phys., Mater., Appl., vol. 12, no. 8, pp. 1370–1375, Aug. 2011.

- [20] L. Li et al., "High-performance and stable organic transistors and circuits with patterned polypyrrole electrodes," Adv. Mater., vol. 24, no. 16, pp. 2159–2164, Apr. 2012.

- [21] J. A. Lansner and T. Lehmann, "Analog CMOS chip set for neural networks with arbitrary topologies," *IEEE Trans. Neural Netw.*, vol. 4, no. 3, pp. 441–444, May 1993.

- [22] T. Shibata and T. Ohmi, "A functional MOS transistor featuring gate-level weighted sum and threshold operations," *IEEE Trans. Electron Devices*, vol. 39, no. 6, pp. 1444–1455, Jun. 1991.

- [23] T. Shibata, H. Kosaka, H. Ishii, and T. Ohmi, "Neuron-MOS neural network using self-learning-compatible synapse circuits," *IEEE J. Solid-State Circuits*, vol. 30, no. 8, pp. 913–922, Aug. 1995.

- [24] E. H. Lee and S. S. Wong, "A 2.5 GHz 7.7TOPS/W switched-capacitor matrix multiplier with co-designed local memory in 40 nm," in *Proc.* IEEE Int. Solid-State Circuits Conf., Jan. 2016, pp. 418–419.

- [25] T. Sakurai and A. R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas," *IEEE J. Solid-State Circuits*, vol. 25, no. 2, pp. 584–594, Apr. 1990.

- [26] O. Marinov, M. J. Deen, U. Zschieschang, and H. Klauk, "Organic thinfilm transistors: Part I—Compact DC modeling," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2952–2961, Dec. 2009.

- [27] M. J. Deen, O. Marinov, U. Zschieschang, and H. Klauk, "Organic thinfilm transistors: Part II—Parameter extraction," *IEEE Trans. Electron Devices*, vol. 56, no. 12, pp. 2962–2968, Dec. 2009.

- [28] K. Fukuda et al., "Organic pseudo-CMOS circuits for low-voltage large-gain high-speed operation," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1448–1450, Oct. 2011.

A. K. M. Mahfuzul Islam (S'11–M'14) received the B.E. degree in electrical and electronics engineering, the M.E. degree in communications and computer engineering, and the Ph.D. degree in informatics, all from Kyoto University, Kyoto, Japan, in 2009, 2011, and 2014, respectively.

He has been a Research Fellow of Japan Society for the Promotion of Science from 2013 to 2015. Since 2015, he has been a Research Associate at the Institute of Industrial Science, the University of Tokyo. His current research interests include

development of low-cost and low-power on-chip sensor circuits, transistor variability characterization and modeling, low-power design techniques, and large-area flexible electronics.

Masamune Hamamatsu (M'16) received the B.S. degree in physics and electronics from Osaka Prefecture University, Osaka, Japan, in 2012, and the M.S. degree in electronic engineering from University of Tokyo, Tokyo, Japan, 2016.

In 2016, he joined SONY Corporation, Tokyo, Japan. He has been engaged in research and development to CMOS analog LSIs. His current research interests are in analog CMOS integrated circuits for low-power circuits.

**Tomoyuki Yokota** was born in Japan, in 1985. He received the M.S. and Ph.D. degrees in applied physics from the University of Tokyo, Tokyo, Japan, in 2010 and 2013, respectively.

Since 2016, he has been a Lecturer in the Department of Electrical and Electronic Engineering, University of Tokyo. His research interests include printed electronics, organic circuits, flexible electronics.

Sunghoon Lee received the M.S. degree in electrical engineering from The University of Tokyo, Tokyo, Japan, in 2011. He is currently working toward the Ph.D. degree in electrical engineering at The University of Tokyo, Tokyo, Japan.

**Wakako Yukita** was born in Japan, in 1978. She received the B.S. degree in food science from the Rakuno Gakuen University, Hokkaido, Japan, in 2002.

Since 2013, she has been a technical assistant in the Department of Electrical and Electronic Engineering, University of Tokyo. Her research interests include printed electronics and organic electronics.

**Makoto Takamiya** (S'98–M'00–SM'14) received the B.S., M.S., and Ph.D. degrees in electronic engineering from the University of Tokyo, Japan, in 1995, 1997, and 2000, respectively.

In 2000, he joined NEC Corporation, Japan, where he was engaged in the circuit design of high-speed digital LSIs. In 2005, he joined University of Tokyo, Japan, where he is an Associate Professor of VLSI Design and Education Center. From 2013 to 2014, he stayed at University of California, Berkeley as a visiting scholar. His research interests include the

design of low-power RF circuits, ultra low-voltage logic circuits, low-voltage power management circuits, and large-area and flexible electronics with organic transistors.

Dr. Takamiya is a member of the technical program committee of IEEE International Solid-State Circuits Conference and IEEE Symposium on VLSI Circuits. He received 2009 and 2010 IEEE Paul Rappaport Awards and the best paper award in 2013 IEEE Wireless Power Transfer Conference.

**Takao Someya** (M'03) received the Ph.D. degree in electrical engineering from The University of Tokyo, Tokyo, Japan, in 1997.

In 1997, he joined the Institute of Industrial Science (IIS), The University of Tokyo, as a Research Associate and was appointed to be a Lecturer of the Research Center for Advanced Science and Technology (RCAST), The University of Tokyo, in 1994, and an Associate Professor of RCAST in 2002. From 2001 to 2003, he worked for the Nanocenter (NSEC) of Columbia University and Bell Labs,

Lucent Technologies, as a Visiting Scholar. From 2003 to 2009, he was an Associate Professor in the Department of Applied Physics and Quantum-Phase Electronics Center, The University of Tokyo. Since 2009, he has been a Professor of Electrical and Electronic Engineering, The University of Tokyo. His current research interests include organic transistors, flexible electronics, plastic integrated circuits, large-area sensors, and plastic actuators.

Dr. Someya is a member of the Materials Research Society (MRS) and the Japanese Society of Applied Physics.

**Takayasu Sakurai** (S'77–M'78–SM'01–F'03) received the Ph.D. degree in electrical enginnering from the University of Tokyo, Tokyo, Japan, in 1981.

In 1981 he joined Toshiba Corporation, where he designed CMOS DRAM, SRAM, RISC processors, DSPs, and SoC Solutions. He has worked extensively on interconnect delay and capacitance modeling known as Sakurai model and alpha power-law MOS model. From 1988 through 1990, he was a visiting researcher at the University of

California Berkeley, where he conducted research in the field of VLSI CAD. From 1996, he has been a professor at the University of Tokyo, working on low-power high-speed VLSI, memory design, interconnects, ubiquitous electronics, organic ICs and large-area electronics. He has published more than 600 technical publications including 100 invited presentations and several books and filed more than 200 patents.

Dr. Sakurai is the Executive Committee Chair for VLSI Symposia and a Steering Committee Chair for the IEEE A-SSCC. He served as a Conference Chair for the Symposium on VLSI Circuits, and ICICDT, a Vice Chair for ASPDAC, a TPC Chair for the A-SSCC, and VLSI Symposium, an executive committee member for ISLPED and a program committee member for ISSCC, CICC, A-SSCC, DAC, ESSCIRC, ICCAD, ISLPED, and other international conferences. He is a recipient of 2010 IEEE Donald O. Pederson Award in Solid-State Circuits, 2009 and 2010 IEEE Paul Rappaport award, 2010 IEICE Electronics Society award, 2009 IEICE achievement award, 2005 IEEE ICICDT award, 2004 IEEE Takuo Sugano award and 2005 P&I patent of the year award and four product awards. He delivered keynote speech at more than 50 conferences including ISSCC, ESSCIRC and ISLPED. He was an elected AdCom member for the IEEE Solid-State Circuits Society and an IEEE CAS and SSCS distinguished lecturer. He is also a domain research supervisor for nano-electronics area in Japan Science and Technology Agency. He is an IEICE Fellow.